- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

MPC55xx,FMPLL,Loss-of-clock

Hello NXP:

MPC55xx,External Reference Mode-- 16MHz , and the system clock is 132MHz.

The other SYNCR's configuration is as follows:

FMPLL_SYNCR[LOCEN] = 0;

FMPLL_SYNCR[LOLRE] = 0;

FMPLL_SYNCR[LOCRE] = 0

If the external clocks fall below the threshold frequency, what the system will happen ? stop ,or enter self-clock mode ?

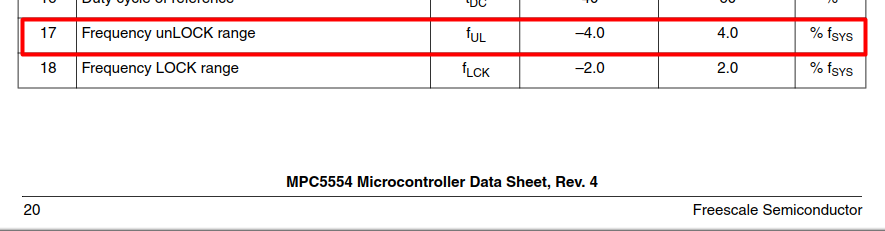

Hi, Regarding loss-of-lock (frequency changes out of specified range) :

While the FMPLL is in an unlocked condition, the system clocks continue to be sourced from the FMPLL as the FMPLL attempts to re-lock. Consequently, during the re-locking process, the system clock frequency is not well defined and may exceed the maximum system frequency thereby violating the system clock timing specifications. Thus it is potentially dangerous configuration and it is recommended to have enabled reset reaction.

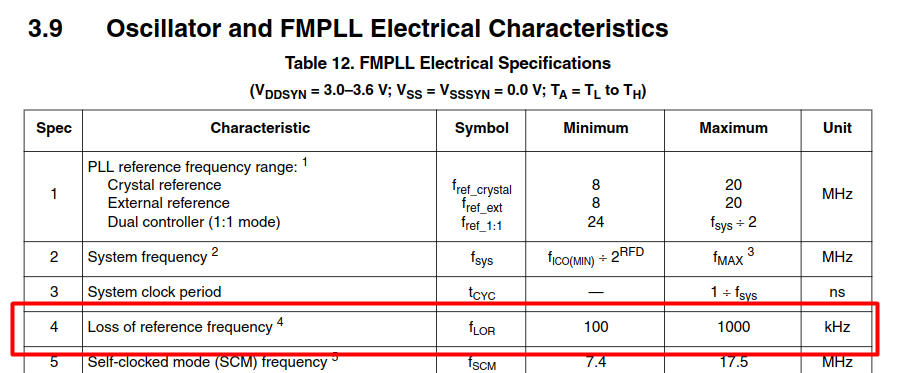

Regarding loss-of-clock (clock dissapears):

Loss of reference frequency is defined as the reference frequency detected internally, which transitions the PLL into self-clocked mode. Again it is recommended to have enabled reset for this event.

Hi,

In the Reference Manual : 11.4.2.6.1 Alternate/Backup Clock Selection

"If the user enables loss of clock by setting FMPLL.SYNCR[LOCEN] =1, then the FMPLL will transition

system clocks to a backup clock source in the event of a clock failure as per Table 11-9."

My question is: If Loss-of-clock disabled ( FMPLL.SYNCR[LOCEN] =0),and then the external clock (16MHz) dissapear, the FMPLL will also enter self-clock mode (SCM) ? or what will happen? It seems that the content is not explained in the manual.

Hi,David :

External Reference Mode(16MHz), system clock is 132MHz , and FMPLL.SYNCR[LOCEN] =0 .

First , power-up the board , the MPC5554 run @ 132MHz , and then I disabled the OSC (external clock dissapear) , but the MCU is still running ,the system clock is lower (~62MHz) .

Why ?