- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Inquiries about Flash ECC Test for MPC5777C

Dear NXP Engineers,

I am checking the 1 or 2 bit ECC error detection function by referring to the application note(Error Correction Codes Implemented on MPC5777C or MPC5775B/E) you provided.

Regarding that, I have two questions.

1. If adress 0x00400060 is read, an interrupt is generated by the 2-bit Error Detection condition, but if adress 0x00400040 is read, an interrupt is not generated by the 1-bit Error Correction condition.

In the application note, there are no other conditions other than the Read of 0x00400040 area to inject 1 bit error. Is an additional procedure required for 1-bit error injection?

2. After injection of 2-bit error detection, it seems that exception handlers are continuously generated when the CPU reads FCCU-related registers. If this is a normal operation, what should I do to stop exception handler from occurring continuously?

I look forward to your reply.

thank you

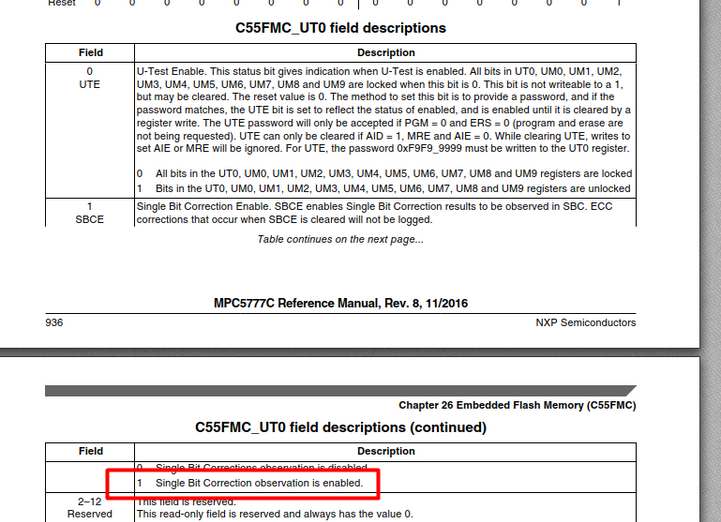

1) Single-bit error reporting needs to be enabled by SBCE bit. It is stated in section 9.3 of mentioned document.

2) I need to add FCCU chapter, as these examples codes does not use FCCU at all, it is also option. If FCCU is used, it is needed to handle FCCU alarm/fault as well. At this moment I would recommend to see following appnotes, where using of FCCU is described:

Using FCCU on MPC5744P:

https://www.nxp.com/docs/en/application-note/AN5284.pdf

and

Error Correction Codes Implemented on MPC5744P:

https://www.nxp.com/docs/en/application-note/AN13179.pdf