- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

I am configuring the watchdog and through my testing it seems to only reset the micro once. Once it has timed out and reset once it won't reset again when trapped in an infinite loop.

My config info

- On entry the TCR register is configured with the value of 0x60140000

- The WRC has a value of 2

- The time base is enabled in HID0

I feel like I am forgetting to clear or check something but I am struggling to find what that is. Some of my confusion may lie in my understanding of the relationship between the p_wrs[0:1] signals and p_reset_b and how it causes the reset.

If you have any questions please let me know.

已解决! 转到解答。

I have solved the problem. I was working under the assumption that the FCCU was defaulting to a hardware recoverable fault in the FCCU_NCF_CFGn register and therefore clearing the status bit in the FCCU_NCF_Sn register on reset. But this is not the case, it is a software recoverable fault. By clearing the status flag bits on initialisation the device is resetting every time it gets stuck in the infinite loop.

Notes:

* The FCCU_NCF_Sn is cleared by writing ones to it. The reference manual does not make this explicit.

Hello,

Thanks for the reply. The SWT module is disabled (it is done with the standard code found in startup.S). And I am only using the core watchdog. My infinite loop is in main() after the configuration.

Hello Peter,

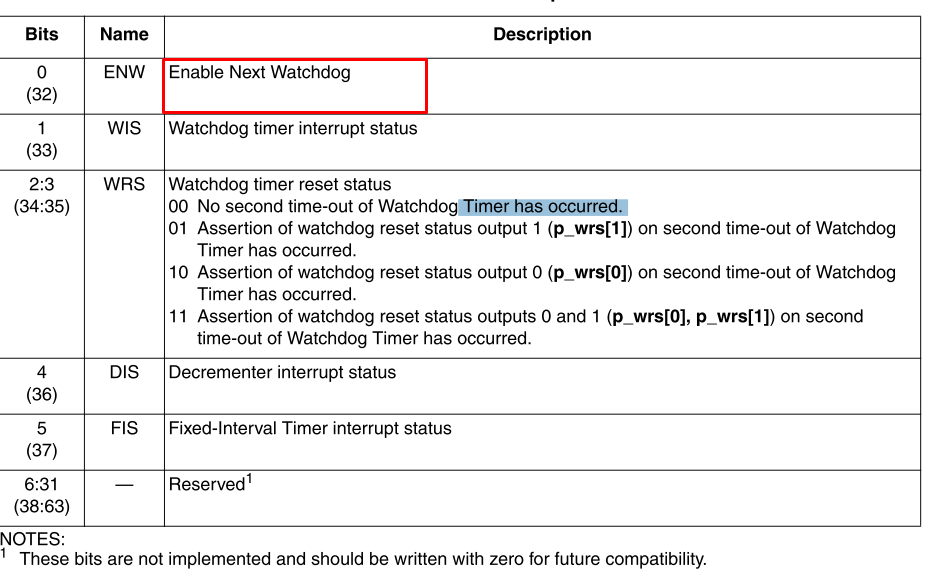

From what I can tell from the e200z7 core manual, the way to enable the watchdog is to set WRC of the TCR register to one of the non-zero values. As mentioned above, I am setting it to 2. Because TSR is read only, its values (including ENW) can only be cleared. I have tried clearing and not clearing it when servicing the watchdog and neither seems to have an effect.

Below is the rough flow of what I am doing. If I remove the infinite loop the service watchdog works.

// Pre main()

...

// Init the TCR register to 0x60140000. This enables the core watchdog

...

e_b main

void main()

{

...

service_watchdog();

...

for(;;){} // Infinite loop to test the watchdog reset.

...

for(;;) // Real main loop

{

...

service_watchdog();

...

}

}

void service_watchdog()

{

// This writes 0x40000000 to the TSR register.

}I have some additional info that maybe relevant/useful if you are still interested in this problem.

As a workaround, I was going to set up the SWT module to act as my watchdog but when I performed the same test as I am doing with the core watchdog, I get the same result, it only resets once.

So at the moment I am going over my configuration of the FCCU. It is the one thing that I can find in common between them and it also controls the reset. I had previously decided that the default values for the FCCU are correct for my needs so I have not written anything explicitly for it.

I have also noticed with the core watchdog that after the first reset, I can see in TSR[WRS] that it is set to 2 (this means that the p_wrs[1] signal has been asserted for reset). But I do not see the corresponding bit in the Noncritical Fault Status (FCCU_NCF_Sn) register set. I cannot see anything similar with the SWT because there doesn't appear to be status info about the reset signal.

If you have any questions please let me know.

I have solved the problem. I was working under the assumption that the FCCU was defaulting to a hardware recoverable fault in the FCCU_NCF_CFGn register and therefore clearing the status bit in the FCCU_NCF_Sn register on reset. But this is not the case, it is a software recoverable fault. By clearing the status flag bits on initialisation the device is resetting every time it gets stuck in the infinite loop.

Notes:

* The FCCU_NCF_Sn is cleared by writing ones to it. The reference manual does not make this explicit.