- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

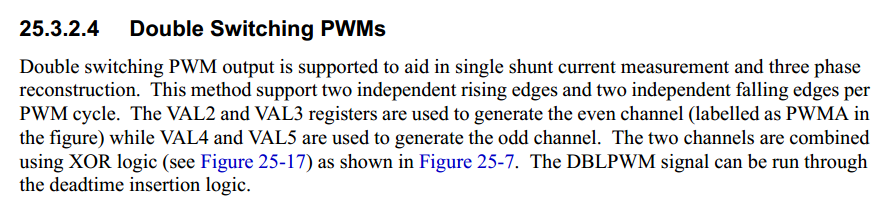

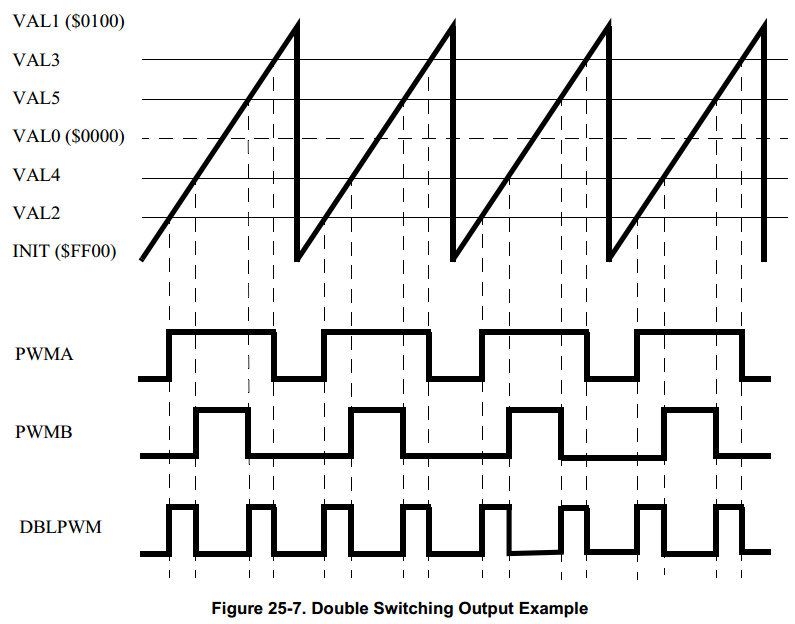

Double Switching PWMs

My chip is MPC5643L. In the "center-aligned and complementary PWM" mode, the IPOL bit of the register MCTRL is 0, the PWMB is from the complementary pair, and the VAL4 and VAL5 are unused. Can I use the "double switch" function in this mode?

Hi,

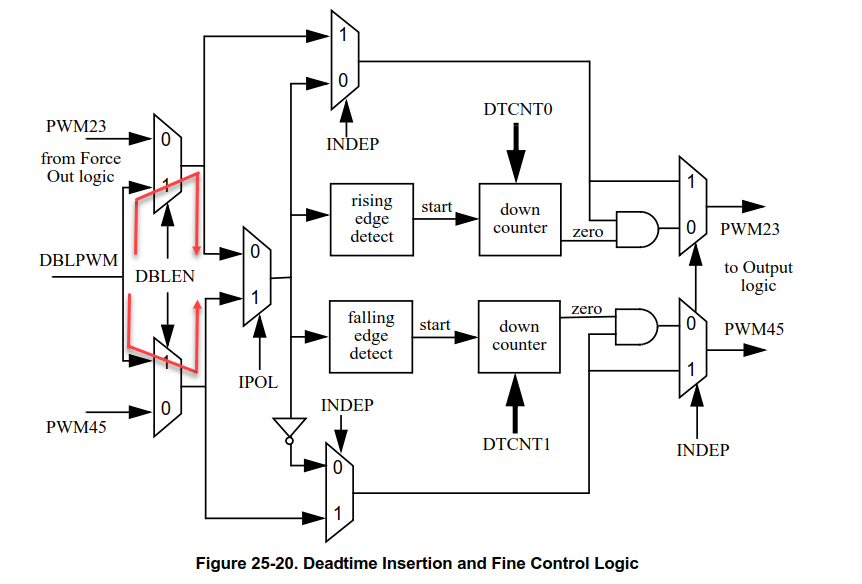

yes, you can. If double switching is enabled (CTRL1[DBLEN]=1), then the DBLPWM signal is used for deadtime logic, regardless of setting the MCTRL[IPOLx] and complementary signals will be generated based on DBLPWM.

BR, Petr

Hi,

LDMOD bit specify when the buffered registers are loaded with new value.

For LDMOD=1 registers are loaded and take effect immediately after LDOK is set,

for LDMOD=0 reagisters are loaded and take effect at the next PWM reload if LDOK is set.

So the PWM will be generated depending on time when LDOK is set. With LDMOD=1 you can simply miss the edge.

BR. Petr

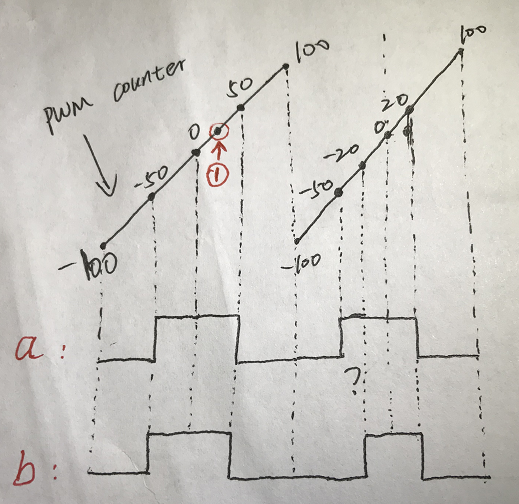

Thank you. Ask another question, I write 0x0C05 to register CTRL1. The PWM register INIT is -100, the register VAL0 is 0, the register VAL1 is 100. In the red circle 1, I calculate the duty cycle is 20%, and the PWM waveform should be a or b or something else, as shown in the following figure. The reference manual is a bit questionable. I mainly want to know how LDMOD affects PWM.