- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear expert:

It seems that the standby mode is not mentioned in 5744PRM document. Doer 5744 have that mode?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

MPC5744P doesn not have standby mode.

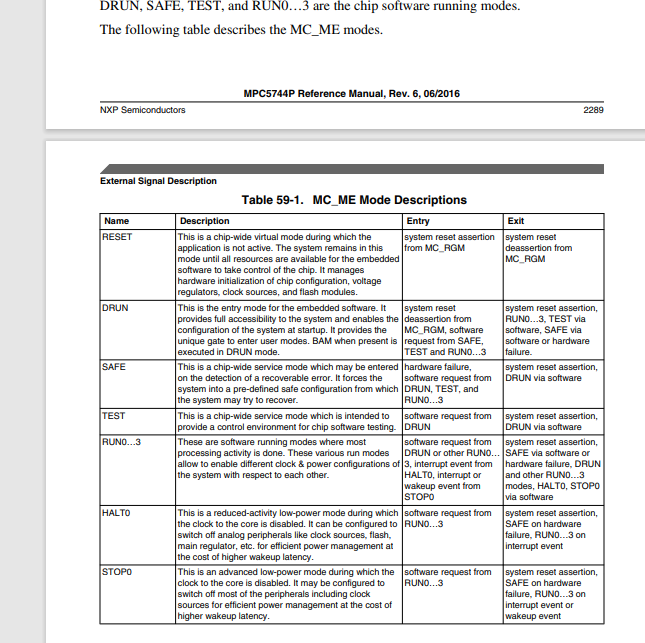

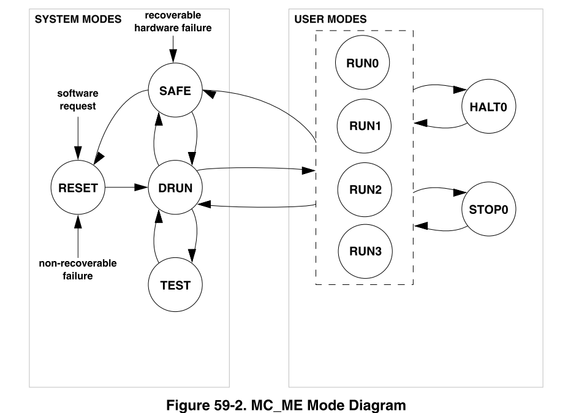

59.4.2.6 HALT0 Mode

This mode is intended as a first-level low-power mode with

• the core clocks frozen the additional core clocks frozen

• XBAR masters cannot operate in system HALT0 mode as they are clock gated. Also,

NPC should be enabled if mode transition is initiated while debugger is connected

• only a few peripherals running

and to be used by software

• to wait until it is required to do something and then to react quickly (i.e., within a few

system clock cycles of an interrupt event)

59.4.2.7 STOP0 Mode

This mode is intended as an advanced low-power mode with:

• the core clock frozen

• the additional core clocks frozen

• XBAR masters cannot operate in system STOP0 mode as they are clock gated. Also,

NPC should be enabled if mode transition is initiated while debugger is connected

• almost all peripherals stopped

So in case you are for example waiting for some external event (measurement, etc...) you will need HALT mode (where core is only frozen) but peripherals are running with clock. For example DMA control of measurements from ADC and CTU with no core interventions.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

MPC5744P doesn not have standby mode.

59.4.2.6 HALT0 Mode

This mode is intended as a first-level low-power mode with

• the core clocks frozen the additional core clocks frozen

• XBAR masters cannot operate in system HALT0 mode as they are clock gated. Also,

NPC should be enabled if mode transition is initiated while debugger is connected

• only a few peripherals running

and to be used by software

• to wait until it is required to do something and then to react quickly (i.e., within a few

system clock cycles of an interrupt event)

59.4.2.7 STOP0 Mode

This mode is intended as an advanced low-power mode with:

• the core clock frozen

• the additional core clocks frozen

• XBAR masters cannot operate in system STOP0 mode as they are clock gated. Also,

NPC should be enabled if mode transition is initiated while debugger is connected

• almost all peripherals stopped

So in case you are for example waiting for some external event (measurement, etc...) you will need HALT mode (where core is only frozen) but peripherals are running with clock. For example DMA control of measurements from ADC and CTU with no core interventions.

Best regards,

Peter

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告