- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- MCX Microcontrollers

- :

- SDK_2_16_000_FRDM-MCXA153 API(CLOCK_FROHFTrimConfig()) Bug

SDK_2_16_000_FRDM-MCXA153 API(CLOCK_FROHFTrimConfig()) Bug

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SDK_2_16_000_FRDM-MCXA153 API(CLOCK_FROHFTrimConfig()) Bug

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

0 is not written in FIRCCSR.LK, so the remaining bits cannot be modified.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear @lmst-mcu ,

From the MCX A153 Reference Manual 22.6.3.1, we can find that FIRC normal configuration write 0 to FIRCCSR[LK] to unlock FIRCCSR.

And I find that in my MCXA153 SDK 2.16 configuration, the register in fsl_clock.c has been successfully unlocked.

Could you please tell me where the problem lies in your case?

Best Regard

Liu

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi. @Alphabert_Liu

Thank you for the response.

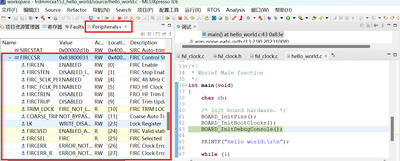

Here is a screenshot of my file contents (full file attached), it seems that the LK bit is not cleared in this function.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @lmst-mcu ,

In my understanding, the default value of the LK bit is 0, and in the following code, the LK bit of this register is also set to 0.

/* Set trim mode. */

SCG0->FIRCCSR = (uint32_t)config.trimMode;You can connect your development board and debug the demo from the SDK you are using. In the debug process, navigate to the FIRCCSR register located within SCG0 in the "Perapherals+" column value of the bit you are interested in.

Best Regard

Liu