- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- レイヤースケープ

- :

- dpmac17 sgmii Problems

dpmac17 sgmii Problems

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

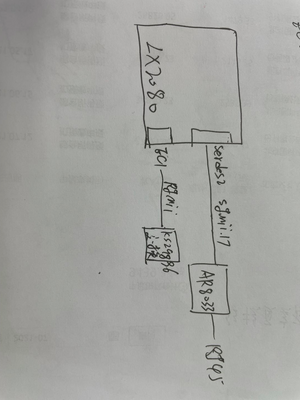

lx2160a custom board。

Using SERDES1 Protocol: 1 (0x1)

Using SERDES2 Protocol: 7 (0x7)

Using SERDES3 Protocol: 3 (0x3)

Now I am using dpMAC17 SGMII of SerDES2 as the debugging network port. The PHY chip is AR0833. Using MII command under uboot, I can see that the PHY is in link state, but ping my host is not working.。

RCW parameter EC1_PMUX[833-832] is changed to 0x01, but the ping still fails

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Would you please provide your u-boot console log and the results of the following commands?

=> mdio list

FSL_MDIO0:

0 - Cortina CS4223 <--> DPMAC2@xlaui4

1 - AR8035 <--> DPMAC17@rgmii-id

2 - AR8035 <--> DPMAC18@rgmii-id

4 - Aquantia AQR107 <--> DPMAC3@xgmii

5 - Aquantia AQR107 <--> DPMAC4@xgmii

FSL_MDIO1:

0 - Inphi in112525_S03P <--> DPMAC6@25g-aui

=> mdio read DPMAC17@rgmii-id 1

Reading from bus FSL_MDIO0

PHY at address 1:

1 - 0x7949

=>

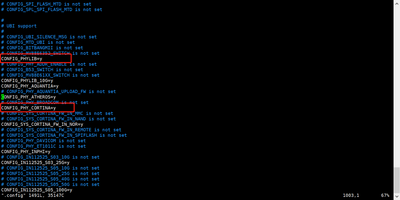

Is your PHY chip AR8033? Have you enabled the following in configs/lx2160ardb_tfa_defconfig

CONFIG_PHYLIB=y

CONFIG_PHY_ATHEROS=y

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

In board/freescale/lx2160a/eth_lx2160ardb.c, please modify the following section according to your custom board.

for (i = WRIOP1_DPMAC17; i <= WRIOP1_DPMAC18; i++) {

interface = wriop_get_enet_if(i);

switch (interface) {

case PHY_INTERFACE_MODE_RGMII:

case PHY_INTERFACE_MODE_RGMII_ID:

dev = miiphy_get_dev_by_name(DEFAULT_WRIOP_MDIO1_NAME);

wriop_set_mdio(i, dev);

break;

default:

break;

}

Modify to:

for (i = WRIOP1_DPMAC17; i <= WRIOP1_DPMAC18; i++) {

interface = wriop_get_enet_if(i);

switch (interface) {

case PHY_INTERFACE_MODE_SGMII:

dev = miiphy_get_dev_by_name(DEFAULT_WRIOP_MDIO1_NAME);

wriop_set_mdio(i, dev);

break;

default:

break;

}

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes, we have modified this part code , The problem remains。Does the DPC need to be modified? We have checked the content of the DPC and there seems to be no problem

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

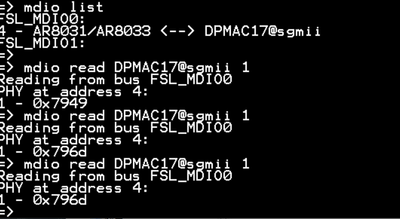

You could use mdio read command to check the status of a SGMII link.

=> mdio list

FSL_MDIO0:

4 - AR8031/AR8033 <--> DPMAC17@sgmii

FSL_MDIO1:

=> mdio read DPMAC17@sgmii 1

Reading from bus FSL_MDIO0

PHY at address 4:

1 - 0x7969

=>

The link partner link status bit is in Register #1 on the PHY. The 'Link Status' bit is bit #2 (from the left) of the last nibble. In your above result, the nibble of interest is "9" (d = b'1001'), and therefore the 'Link Status' = 0, which means 'link download'. If the link is up, this bit would be a "1," and we would see 0x796d.

So on your custom board the SGMII link status is download, please check the probable hardware issue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

The second read was link.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Few clarifications:

- Do ping works on MAC18?

- Few strange observation in U-boot log:

(a). Clock configuration shown in uboot is not as per the selected protocol.

(b). PCA: failed to select proper channel

MAC17 and MAC18 is same so same issue should be with MAC 18.

- Can you share share schematic?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

1. Do ping works on MAC18?

Re:

Dpmac18 (EC2) cannot be tested because it is not connected to any PHY.We only used mac17, our SERDES2's SGMII17 was connected to the AR8033, and our EC1 was connected to the KSZ9896 switch chip via RGMII.I think this might be a problem, so I'm just going to debug SGMII and leave RGMII alone for now

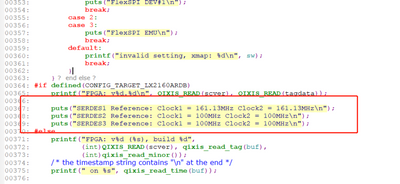

(a). Clock configuration shown in uboot is not as per the selected protocol.

Re: The clock configuration is printed directly in the source code, we did not remove, serdes2 clock is actually 161.xxxMhz.

(b). PCA: failed to select proper channel

Re: Our custom board is not using PCA9547 (I2C MUX, level 1), so there is this error。

schematic:

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

What is the status of link status between MAC and PHY?

You can check this as detail below:

On U-boot prompt:

printenv elf_load

elf_load=dcache off; tftp 0x80300000 <location of mdio>/mdio.bin; dcache on;

run elf_load

go 0x80300000 read 0x8c47000 3 {0x8c47000: MAC 17 Base address}

a valid PCS link ix 0x00000004

bit 2 set

Please let us know .

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I followed your prompts and programmed mdio.bin to 0x80300000, then read the MAC 17 Base address and got some values.

=> md 0x8c47000 4

08c47000: 00010200 00000000 00000810 00000000 ................

=>

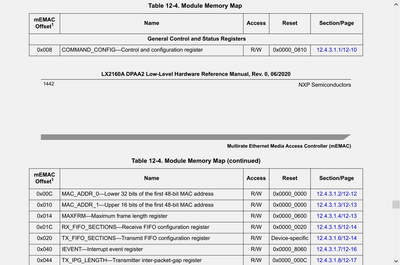

I looked at the manual "LX2160ADPAA2RM. PDF "and did not see the register about the MAC link status

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please read using below command

go 0x80300000

read 0x8c47000 3

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

the usage is a little wrong. One parameter missing?

=> go 0x80300000 read 0x8c47000 3

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 4

operation = "read"

mac offset = "0x8c47000"

dev addr = "3"

Usage: go 0x80300000 <read|write> <mac offset> <mmd> <reg> [data]

## Application terminated, rc = 0x0

——------------------------------------------------------------------------------------

=> go 0x80300000 read 0x8c47000 3 0

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c47000"

dev addr = "3"

reg addr = "0"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000000

## Application terminated, rc = 0x0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Sorry for typo, correct command is

go 0x80300000 read 0x8c0b000 3 1

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

MAC and PHY link status is not ok? We are using SGMII, DPL or DPC need configuration ?

=> go 0x80300000 read 0x8c0b000 3 1

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "1"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000000

## Application terminated, rc = 0x0

=> go 0x80300000 read 0x8c47000 3 1

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c47000"

dev addr = "3"

reg addr = "1"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000000

## Application terminated, rc = 0x0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for update. Can you please view more registers to check if read is working correctly?

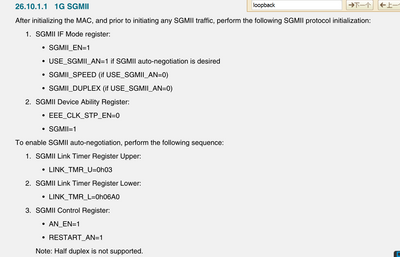

Please refer register details in LX2160ARM Rev0 07/2020 section 26.9.2 SGMII Registers (Please read register 0,2,3 also)

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

A little problem

=> mdio list

FSL_MDIO0:

4 - AR8031/AR8033 <--> DPMAC17@sgmii

FSL_MDIO1:

=> mdio read DPMAC17@sgmii 1

Reading from bus FSL_MDIO0

PHY at address 4:

1 - 0x796d

=> go 0x80300000 read 0x8c0b000 3 2

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "2"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000000

## Application terminated, rc = 0x0

=> go 0x80300000 read 0x8c0b000 3 3

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "3"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000000

## Application terminated, rc = 0x0

=> go 0x80300000 read 0x8c0b000 3 0

## Starting application at 0x80300000 ...

Example expects ABI version 9

Actual U-Boot ABI version 9

Internal MDIO read / write

argc = 5

operation = "read"

mac offset = "0x8c0b000"

dev addr = "3"

reg addr = "0"

mdio_cfg bsy set

mdio_data bsy set

output data: 0x00000000

## Application terminated, rc = 0x0

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please refer "Table 51 MAC Capabilities" This table shows different MAC address and there capability.

I understand customer is using MAC 17 hence to reading all the register customer needs to use address "8C4_7000h"

Syntax for Clause 45: (Please read status register multiple times)

go 0x80300000 read <mac address> <MMD device> <register>

go 0x80300000 read 0x8c0b000 3 1

0x8c0b000= MAC address

3-> Device: PCS address (Table 287. Device Address Overview)

1-> PCS status register

Syntax for Clause 22: (Please read status register multiple times)

read <mac_addr> <mmd always 0> <reg addr> <any value: e.g. 0 this is a switch that tells its clause 22>

For example to read control register

go 0x80300000 read 0x8c47000 0 0 0

To Read status register

go 0x80300000 read 0x8c47000 0 1 0

Do customer is able to boot linux on board?

does ping don't work on Linux?

Can you detail about your setup?

Please use MAC17 address "8C4_7000" instead of 0x8c0b000.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Yiping,

Could you help give a demo for mac loopback code in u-boot.

Such as mac17 mac loopback. Many thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hi yipingWang

1:

crc32+

fsl-mc: Booting Management Complex ... SUCCESS

fsl-mc: Management Complex booted (version: 10.24.0, boot status: 0x1)

Hit any key to stop autoboot: 0

2:

=> mdio list

FSL_MDIO0:

4 - AR8031/AR8033 <--> DPMAC17@sgmii

FSL_MDIO1:

=> mii read 4 5

CDE1

=> mii read 4 5

CDE1

=> mii dump

5. (cde1) -- Autonegotiation partner abilities register --

(8000:8000) 5.15 = 1 next page able

(4000:4000) 5.14 = 1 acknowledge

(2000:0000) 5.13 = 0 remote fault

(1000:0000) 5.12 = 0 (reserved)

(0800:0800) 5.11 = 1 asymmetric pause able

(0400:0400) 5.10 = 1 pause able

(0200:0000) 5. 9 = 0 100BASE-T4 able

(0100:0100) 5. 8 = 1 100BASE-X full duplex able

(0080:0080) 5. 7 = 1 100BASE-TX able

(0040:0040) 5. 6 = 1 10BASE-T full duplex able

(0020:0020) 5. 5 = 1 10BASE-T able

(001f:0001) 5. 4- 0 = 1 partner selector = IEEE 802.3 CSMA/CD

3:

CLK_SD2_F_P/N is 100Mhz

can you provide a demo of dpmac17 sgmii disable auto-negotiation ?