- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- Re: Does the LS1046a support the Arm CoreLink CCI-400 Performance monitoring unit (PMU)?

Does the LS1046a support the Arm CoreLink CCI-400 Performance monitoring unit (PMU)?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does the LS1046a support the Arm CoreLink CCI-400 Performance monitoring unit (PMU)?

The LS1046a RM manual mentions the "CCI-400 PMU", while it does not describe the registers of the "CCI-400 PMU". Note the "CCI-400 PMU" is not the PMU in Arm® Cortex®-A72 core.

The LS1046a RM manual mentions the "CCI-400 PMU"

section "1.4.2 Arm CoreLink CCI-400 Cache Coherent Interconnect" mentioned

"• Performance monitoring unit (PMU) to count performance-related events"

Section "9.6.3 Speculative fetch" mentioned

"You can use the PMU to record the number of retry transactions for each master interface."

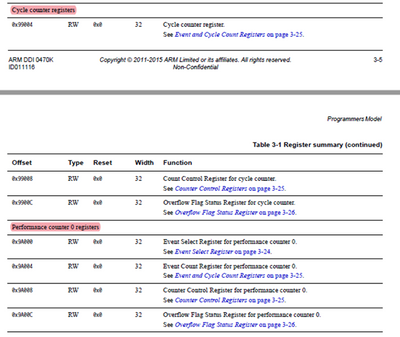

LS1046A RM "9.5.1 CCI400 Registers memory map" doe not has the PMU register as in ARM® CoreLink™ CCI-400 Cache Coherent Interconnect Revision: r1p5

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

LS1046a supports the Arm CoreLink CCI-400 Performance monitoring unit (PMU).

Please refer to the CCI-400 ARM document bundled with the LS1046ARM - ARM® CoreLink™ CCI-400 Cache Coherent Interconnect Revision: r1p5 Technical Reference Manual.

There seems to be ambiguity in the LS1046ARM because CCI-400 has its own PMU.

Offset 0x90000 in the ARM CCI-400 TRM corresponds to the CCSR address 0x1180000 of the LS1046A.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

LS1046a supports the Arm CoreLink CCI-400 Performance monitoring unit (PMU).

Please refer to the CCI-400 ARM document bundled with the LS1046ARM - ARM® CoreLink™ CCI-400 Cache Coherent Interconnect Revision: r1p5 Technical Reference Manual.

There seems to be ambiguity in the LS1046ARM because CCI-400 has its own PMU.

Offset 0x90000 in the ARM CCI-400 TRM corresponds to the CCSR address 0x1180000 of the LS1046A.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did further test and be able to use the CCI-400 PMU on LS1046a .

Thanks!