- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- LPC824 SCTimer cannot unset the CTRL::STOP bit flag

LPC824 SCTimer cannot unset the CTRL::STOP bit flag

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC824 SCTimer cannot unset the CTRL::STOP bit flag

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Right after clearing the CTRL::HOLD bit flag (in order to start the timer), the CTRL::STOP bit flag is automatically set, and there's no way to clear it!

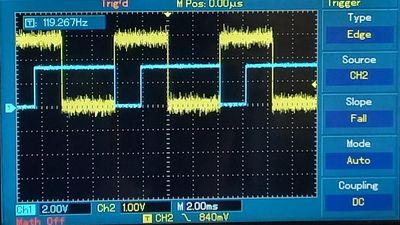

This same application runs nicely on a LPC812MAX board:

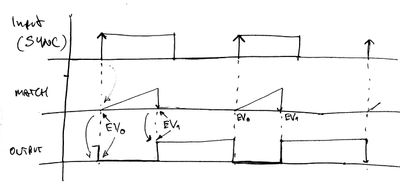

A synchrony signal is shown on yellow color, while an output signal is shown in blue color. What I'm trying to achieve is (which I've already done it in the LPC812 uC):

The problem with the LPC812 is that you forgot to include an ADC, so for my application I needed to find a similar device.

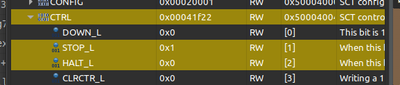

Now, what's the problem with the LPC824? Let me show you the last instruction after the timer has been configured:

//Chip_SCT_ClearControl( LPC_SCT, SCT_CTRL_HALT_L ); // both instructions are the same

LPC_SCT->CTRL_U &= ~( 4 );

After executing this instruction the CTRL::STOP bit flag is set:

And none of these instructions are capable of clearing the STOP flag:

Chip_SCT_ClearControl( LPC_SCT, SCT_CTRL_STOP_L );

LPC_SCT->CTRL_U &= ~(0x2);

At the end of this post I'll show you the complete code for such configuration; but before in doing so, I found that if I comment this next instruction out, which stops the timer in EVENT1, then the STOP flag is not set; however, my application is still failing at its purpose:

LPC_SCT->STOP_U = SCT_EVT_1;

Thank you in advance. Any hint or suggestion is appreciated.

Here is my code (SystemCoreClock is running at 30MHz):

void sct_fsm_init (void)

{

Chip_SCT_Init(LPC_SCT);

Chip_SCT_Config(LPC_SCT,

SCT_CONFIG_32BIT_COUNTER // 32 bits

| SCT_CONFIG_AUTOLIMIT_L ) // timer resets itself

;

// F=120Hz, steps=1000:

Chip_SCT_SetControl( LPC_SCT,

SCT_CTRL_HALT_L

| SCT_CTRL_CLRCTR_L

| SCT_CTRL_PRE_L( SystemCoreClock/120000 - 1 ) )

;

LPC_SCT->STATE_U = 0;

// no states (UM_LPC812: 10.7.12; UM_LPC824: 16.7.12)

// --------------- EVENT registers ---------------

// *** EVENT 0 ***

LPC_SCT->EV[ SCT_EVENT_0 ].STATE = ENABLE_STATE0;

/* Event 0 only happens in state 0 */

LPC_SCT->EV[ SCT_EVENT_0 ].CTRL =

SCT_OUTSEL_L // inputs

| (0 << 6 ) // CTIN0

| SCT_IOCOND_RAISE

| SCT_COMBMODE_IO // only CTIN0

| SCT_STATELD_0 // no state changes are allowed

| SCT_STATEEV_0

;

LPC_SCT->START_U = SCT_EVT_0;

// EV0 starts the timer

LPC_SCT->OUT[ SCT_OUTPUT_0 ].CLR = SCT_EVT_0;

// EV0 clear the output

// *** EVENT 1 ***

LPC_SCT->EV[ SCT_EVENT_1 ].STATE = ENABLE_STATE0;

// EVT1 habilitado en ST0

LPC_SCT->EV[ SCT_EVENT_1 ].CTRL =

SCT_EVECTRL_MATCH0 // match

| SCT_COMBMODE_MATCH // only match

| SCT_STATELD_0 // state changes are not allowed

| SCT_STATEEV_0

;

Chip_SCT_SetMatchCount( LPC_SCT, SCT_MATCH_0, 250 );

Chip_SCT_SetMatchReload( LPC_SCT, SCT_MATCH_0, 250 );

LPC_SCT->STOP_U = SCT_EVT_1;

// EV1 stops the timer

LPC_SCT->OUT[ SCT_OUTPUT_0 ].SET = SCT_EVT_1;

// EV1 sets the output

//Chip_SCT_ClearControl( LPC_SCT, SCT_CTRL_HALT_L );

LPC_SCT->CTRL_U &= ~( 4 );

}