- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

I am trying to use the NMI in the LPC55S69, and the User Manual has this section:

In the paragraph text it indicates that Table 44 gives "a list of all the peripheral interrupts and their IRQ numbers", however Table 44 (which appears immediately after) is actually a description of the NMISRC register.

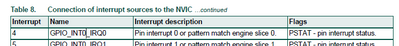

Should it perhaps refer to "Table 8. Connection of interrupt sources to the NVIC" ?

Are those the IRQ numbers that should be used in the NMISRC register?

UPDATE

Edit, so lets say I have PIO1_18 set in the pins config tool for "PIN:PINT,0", and in the Peripherals tool I have it setup for a Falling Edge interrupt event, and I don't "Enable callback/interrupt" (since the 'Remark' in the User Manual above says you shouldn't).

I then disable NMIENCPU0, set IRQCPU0 to '4' (which I think is the correct value based on Table 8), and then re-enable NMIENCPU0:

How do I write the interrupt handler (in C++) for the NMI? - I don't see any examples of what format / structure it should be in?

已解决! 转到解答。

Hi @PhilV

Yes you are correct, the IRQn values can be found on table 8, also you can look at them on the LPC55S69_cm33_core0.h file on a SDK example project.

How do I write the interrupt handler (in C++) for the NMI? - I don't see any examples of what format / structure it should be in?

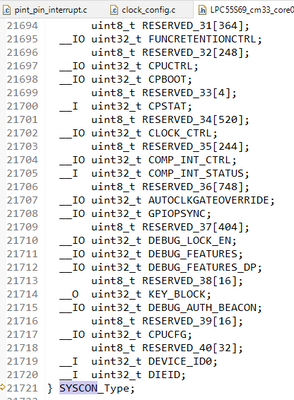

The interrupt handler has to be written on C, and we do not have any examples that enables the NMI on a pin, however you can look into the lpcxpresso55s69_pint_pin_interrupt example and you will have to write the configuration of the NMI on the respective registers, you can look the structure of the SYSCON here:

I have already posted a reply on your other question

I hope it helps.

Best Regards, Miguel.

Many thanks @Miguel04 , the below is now for my reference, and anyone else that follows in my footsteps.

- Connect the GPIO to the PINT peripheral (can do this in Pin Config tool)

- In Peripheral Config tool for PINT configure the interrupt characteristic (falling edge, rising edge etc); do NOT enable the callback / interrupt (otherwise you'll end up potentially trying to handle it twice)

- In main() function reconfigure the NMI registers to map the appropriate PINT interrupt to NMI:

/* Setup NMI interrupt for ANALOG_SW current trip event

*

* According to LPC55 User Manual section 4.5.6:

* To change the interrupt source for the NMI, the NMI source must first be

* disabled by writing 0 to the NMIEN bit. Then change the source by updating the IRQN bits

* and re-enabling the NMI source by setting NMIEN.

*/

SYSCON->NMIsrc=(SYSCON->NMISRC & ~SYSCON_NMISRC_NMIENCPU0_MASK); // DISABLE IT

SYSCON->NMIsrc=(SYSCON->NMISRC & ~SYSCON_NMISRC_IRQCPU0_MASK) | SYSCON_NMISRC_IRQCPU0(PIN_INT0_IRQn); // Set the NMI to PIN_INT0_IRQn

SYSCON->NMIsrc=(SYSCON->NMISRC & ~SYSCON_NMISRC_NMIENCPU0_MASK) | SYSCON_NMISRC_NMIENCPU0(1); // ENABLE IT

- startup_lpc55s69_cm33_core0.cpp describes the ".isr_vector" table, and NMI interrupt can be see as "NMI_Handler"

- Somewhere in your code write the NMI handler - note that if you don't 'hang' in this handler then you must clear the interrupt flag that triggered it (since the standard interrupt handler won't now be doing that for you), otherwise you'll just keep re-entering the NMI handler:

/**

* Handler for the non-maskable interrupt

*/

void NMI_Handler(void)

{

// printf("NMI Handler hit\n");

// Pin specific NMI handling for falling edge

if(PINT_PinInterruptGetFallFlag(PINT, kPINT_PinInt0))

{

// Do useful stuff

// ...

// ...

/* Edge sensitive: clear Pin interrupt */

PINT_PinInterruptClrStatus(PINT, kPINT_PinInt0);

}

}

Hi @PhilV

Yes you are correct, the IRQn values can be found on table 8, also you can look at them on the LPC55S69_cm33_core0.h file on a SDK example project.

How do I write the interrupt handler (in C++) for the NMI? - I don't see any examples of what format / structure it should be in?

The interrupt handler has to be written on C, and we do not have any examples that enables the NMI on a pin, however you can look into the lpcxpresso55s69_pint_pin_interrupt example and you will have to write the configuration of the NMI on the respective registers, you can look the structure of the SYSCON here:

I have already posted a reply on your other question

I hope it helps.

Best Regards, Miguel.