- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC4088 and external SDRAM issues

LPC4088 and external SDRAM issues

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC4088 and external SDRAM issues

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

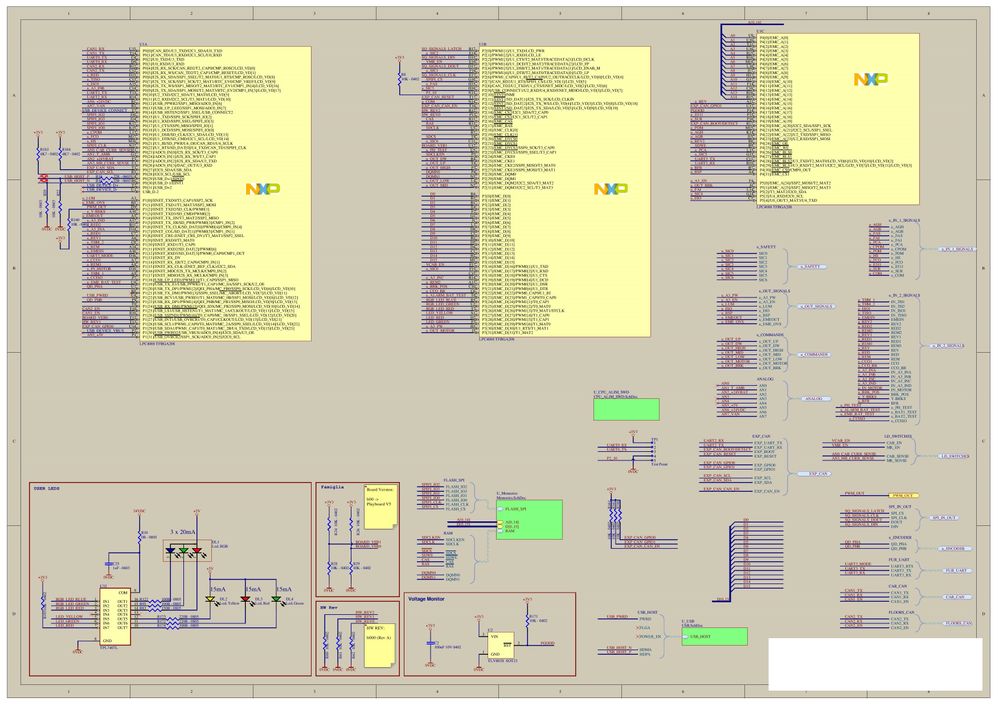

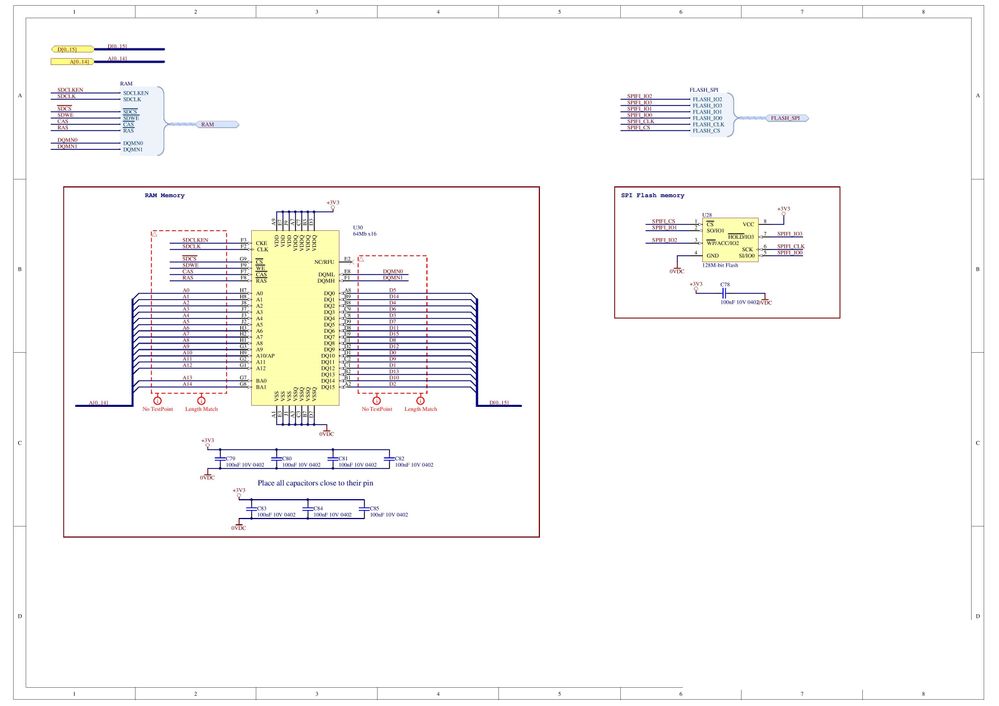

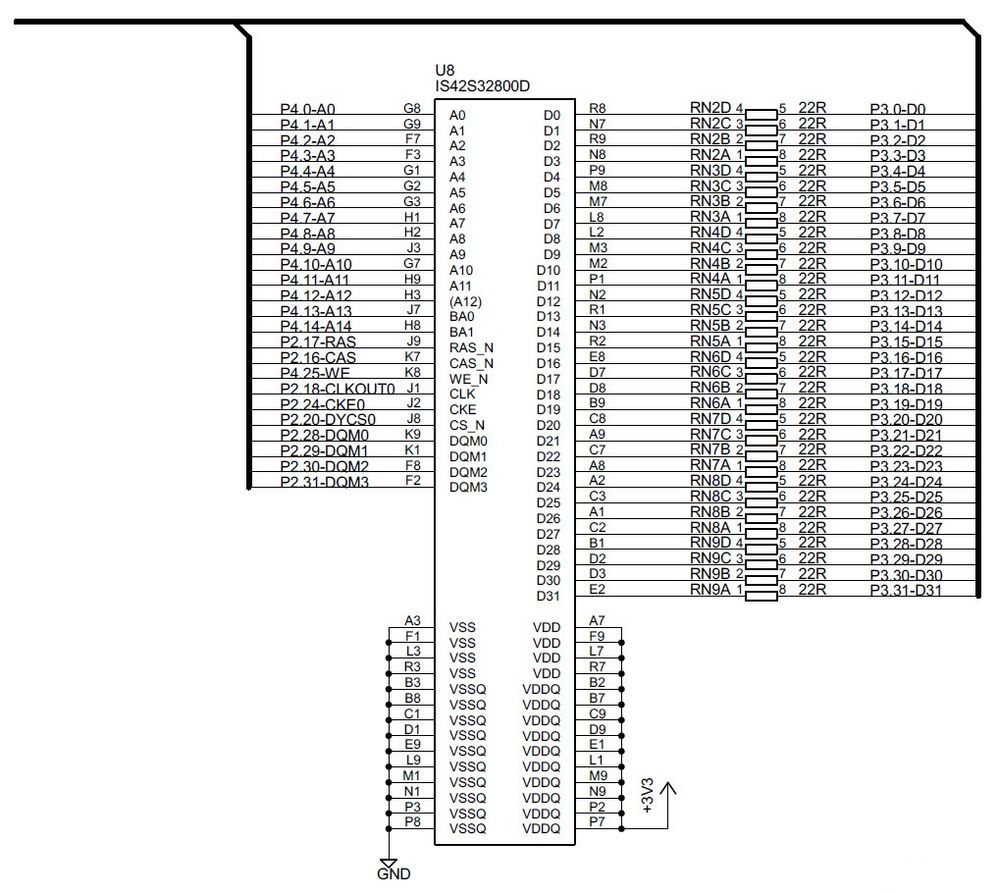

Good morning. I've been working on a custom board based on LPC4088 and external SDRAM chip IS42S16400J, under IAR EWARM 6.70.

The CPU is set to run at 108Mhz and the EMC a 54Mhz.

I'm using the init routines from the LPCOPEN bundle v2.10 (I think it's the latest one).

The chip is mapped to block 0 (address 0xA0000000).

I customized the init structure for my memory chip as follows:

STATIC const IP_EMC_DYN_CONFIG_T IS42S16400J_6BL_config = {

EMC_NANOSECOND(64000000 / 4096),

0x01, /* Command Delayed */

EMC_NANOSECOND(15), /* tRP */

EMC_NANOSECOND(42), /* tRAS */

EMC_NANOSECOND(66), /* tSREX */

EMC_NANOSECOND(15), /* tAPR */ //Using trp

EMC_CLOCK(3), /* tDAL */

EMC_CLOCK(2), /* tWR */

EMC_NANOSECOND(60), /* tRC */

EMC_NANOSECOND(66), /* tRFC */

EMC_NANOSECOND(66), /* tXSR */

EMC_NANOSECOND(12), /* tRRD */

EMC_CLOCK(0x02), /* tMRD */

{

{

EMC_ADDRESS_DYCS0, /* EA Board uses DYCS0 for SDRAM */

2, /* RAS */

EMC_DYN_MODE_WBMODE_PROGRAMMED |

EMC_DYN_MODE_OPMODE_STANDARD |

EMC_DYN_MODE_CAS_2 |

EMC_DYN_MODE_BURST_TYPE_SEQUENTIAL |

EMC_DYN_MODE_BURST_LEN_8,

EMC_DYN_CONFIG_DATA_BUS_16 |

/*EMC_DYN_CONFIG_LPSDRAM |*/

EMC_DYN_CONFIG_4Mx16_4BANKS_12ROWS_8COLS |

EMC_DYN_CONFIG_MD_SDRAM

},

{0, 0, 0, 0},

{0, 0, 0, 0},

{0, 0, 0, 0}

}

};I just added a missing RBC check that I got from LPC43XX sourc code. It's the following:

/* is it high performance RBC mode? */

if (!(Dynamic_Config->DevConfig[ChipSelect].DynConfig & EMC_DYN_CONFIG_LPSDRAM)) {

/* yes, it is */

/* getting the number of banks */

if (!(Dynamic_Config->DevConfig[ChipSelect].DynConfig & (0x7 << EMC_DYN_CONFIG_DEV_SIZE_BIT))) {

/* 2 banks => 1 bank select bit */

Col_len += 1;

}

else {

/* 4 banks => 2 bank select bits */

Col_len += 2;

}

}Well, I think I said everything, but just ask if you need more details. So I can describe "the symptoms".

After initialization of EMC controller and SDRAM chip, my app executes some SDRAM tests that are ALWAYS passed with success. These tests are taken from the LPCOPEN projects mentioned above (mem_tests.c, which contains the walking tests and pattern tests). It also passes succesfully some other tests we had already used in the past.

I'm still in debugging phase of the project, so my code continuously runs some debug checks such as writing some placehoders bytes in my structured variable placed in the external RAM and reads them back. After less than a minute one of this byte is written badly: 0xAF instead of 0xAA. It's deterministic. On the other hand this symptom is raised immediately as soon as I put this structured variable in the "Live Watch" window in IAR. Surely the debugger triggers accesses to the external RAM to show me that variable. This structured variable is about 17Kbytes.

Also, while debugging, I get bad writings at the same positions and with the same bad values.

My attempts to solve the problems were:

- Lower the frequencies of CPU to 60Mhz and EMC to 30Mhz;

- "Playing" a little with the timings of the chip;

- Trying different settings such as RBC and BRC, busrt types...;

In most cases I had no changes and sometimes the tests failed.

Thanks for your time.

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply, @jeremyzhou.

I had already read the discussion you linked, such other one in the community, but I could find anything that could solve my problem.

I also tried again the configuration of timing from your last reply, but they make the tests fail.

Also tried to modify the fine tuning of the clock delay in EMCDLYCTL register.

Also checked again GPIOs to be set to correct functions. Here's the code that inits pins:

#define SDRAM_PIN_IOCON_VALUE 0x201 //Fast slew rate and function 0x01

void BSP_SDRAM_Init(void)

{

// Assign pins to SDRAM controller

//CAS

IOCON_P2_16 = SDRAM_PIN_IOCON_VALUE;

//RAS

IOCON_P2_17 = SDRAM_PIN_IOCON_VALUE;

//SDCLK

IOCON_P2_18 = SDRAM_PIN_IOCON_VALUE;

//SDCS

IOCON_P2_20 = SDRAM_PIN_IOCON_VALUE;

//SDCLKEN

IOCON_P2_24 = SDRAM_PIN_IOCON_VALUE;

//DQMN0..1

IOCON_P2_28 = SDRAM_PIN_IOCON_VALUE;

IOCON_P2_29 = SDRAM_PIN_IOCON_VALUE;

//DATA BUS

IOCON_P3_00 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_01 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_02 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_03 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_04 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_05 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_06 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_07 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_08 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_09 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_10 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_11 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_12 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_13 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_14 = SDRAM_PIN_IOCON_VALUE;

IOCON_P3_15 = SDRAM_PIN_IOCON_VALUE;

//ADDRESS BUS

IOCON_P4_00 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_01 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_02 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_03 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_04 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_05 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_06 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_07 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_08 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_09 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_10 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_11 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_12 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_13 = SDRAM_PIN_IOCON_VALUE;

IOCON_P4_14 = SDRAM_PIN_IOCON_VALUE;

//SDWE

IOCON_P4_25 = SDRAM_PIN_IOCON_VALUE;

/*Init SDRAM controller*/

/* Setup EMC Delays */

/* Move all clock delays together */

LPC_SYSCTL->EMCDLYCTL = (CLK0_DELAY) | (CLK0_DELAY << 8) | (CLK0_DELAY << 16 | (CLK0_DELAY << 24));

/* Init EMC Controller -Enable-LE mode- clock ratio 1:1 */

Chip_EMC_Init(1, 0, 0);

/* Init EMC Dynamic Controller */

Chip_EMC_Dynamic_Init((IP_EMC_DYN_CONFIG_T *) &IS42S16400J_6BL_config);

}I'm attaching schematic images, too.

Still encoutering thos issues.

Thanks,

Marco

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Marco Fratini,

After confirming, the LPC4088 OEM BOARD integrates the SDRAM IS42S32800D whose electrical characteristics are compatible with the IS42S16400J, so I'd highly recommend you to refer to the memtest demo in the lpcopen_2_10_lpcxpresso_ea_devkit_4088.

LPCOpen Software for LPC40XX|NXP

Have a great day,

TIC

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for you reply, jeremyzhou.

The demo project you mentioned was the one I startet from. I changed the IS42S32800D parameters accordingly to my memory chip (like some timings, row bank columns, bus width and so on). My code also performs the mem_tests from the demo (walking0, walking1, etc..). So, I had already tried those values.

The only differences I see from schematics are the series resistors in data lines and the fact that I scrambled the data lines to avoid vias in PCB layout.

But, before thinking about 22R series resistors as possible cause, I'm trying to solve the problem by adjusting software.

As last, the data line scrambling should be safe (we have another board with LPC1788, with data lines scrambled and no resistors, that works fine).

The failure in sdram occurs after a while in free running, or as soon as I observe the sdram from "Live Watch". Rarely it doesn't occur at all.

Thanks,

Marco