- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Software Development Kit

- :

- Re: How to setup clock from external crystal on K64F and KSDK2.1

How to setup clock from external crystal on K64F and KSDK2.1

Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to setup clock from external crystal on K64F and KSDK2.1

03-01-2017

10:26 AM

1,246 Views

mastupristi

Senior Contributor I

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm porting a firmware running on a custom board from KSDK 1.3 to KSDK 2.1. I use Kinetis MK64FN1M0VLQ12 clocked with a 12.288 MHz crystal. With KSDK 1.3 the firmware works fine. With KSDK 2.1 I am not able to correctly setup clock.

void BOARD_BootClockRUN(void) { /* * Core clock: 119.808MHz * Bus clock: 59.904MHz */ const mcg_pll_config_t pll0Config = { .enableMode = 0U, .prdiv = 0x03U, // divide by 4 .vdiv = 0x0fU, // multiply by 39 }; const sim_clock_config_t simConfig = { .pllFllSel = 1U, /* PLLFLLSEL select PLL. */ .er32ksrc=2U, /* ERCLK32K selection, use RTC. */ .clkdiv1 = SIM_CLKDIV1_OUTDIV1(0) | SIM_CLKDIV1_OUTDIV2(1) | SIM_CLKDIV1_OUTDIV3(2) | SIM_CLKDIV1_OUTDIV4(4), }; CLOCK_SetSimSafeDivs(); BOARD_InitOsc0(); CLOCK_BootToPeeMode(kMCG_OscselOsc, kMCG_PllClkSelPll0, &pll0Config); CLOCK_SetInternalRefClkConfig(kMCG_IrclkEnable, kMCG_IrcSlow, 0); CLOCK_SetSimConfig(&simConfig); SystemCoreClock = 119808000U; // 12288000/4 * 39 } void BOARD_InitOsc0(void) { const osc_config_t oscConfig = {.freq = BOARD_XTAL0_CLK_HZ, .capLoad = 0, .workMode = kOSC_ModeOscHighGain, .oscerConfig = { .enableMode = kOSC_ErClkEnable, #if (defined(FSL_FEATURE_OSC_HAS_EXT_REF_CLOCK_DIVIDER) && FSL_FEATURE_OSC_HAS_EXT_REF_CLOCK_DIVIDER) .erclkDiv = 0U, #endif }}; CLOCK_InitOsc0(&oscConfig); /* Passing the XTAL0 frequency to clock driver. */ CLOCK_SetXtal0Freq(BOARD_XTAL0_CLK_HZ); }

firmware hangs in CLOCK_BootToPeeMode().

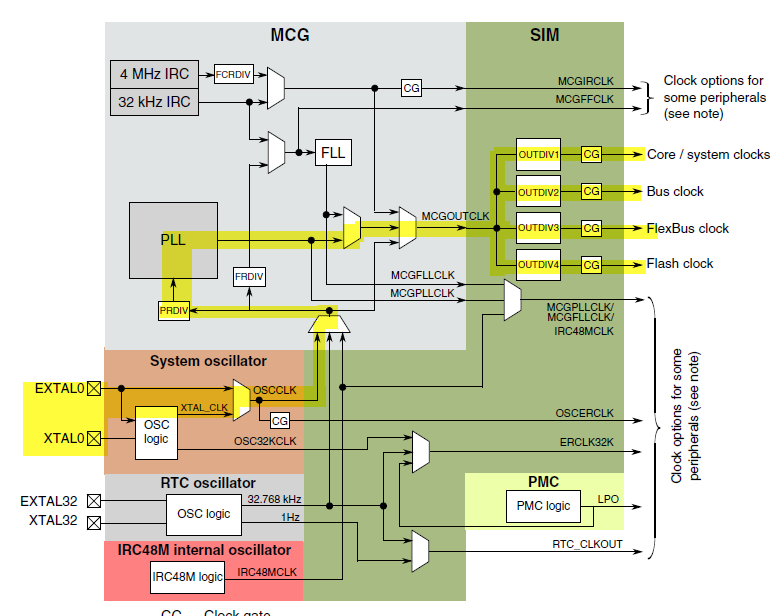

I want to make this clock path:

where am I wrong?

best regards

Max

1 Reply

03-06-2017

01:32 AM

840 Views

NXP Employee

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Max,

there is available Clocks tool on http://mcuxpresso.nxp.com/ that can generate clock tool initialization code for you. This might help. The tool is available both as WEB version and also as DESKTOP version.

Regards

Marek