- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisソフトウェア開発キット

- :

- Re: Can't have SDA completely low at ACK on HAL I2C ,MKV31

Can't have SDA completely low at ACK on HAL I2C ,MKV31

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Can't have SDA completely low at ACK on HAL I2C ,MKV31

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi to all the people in the community

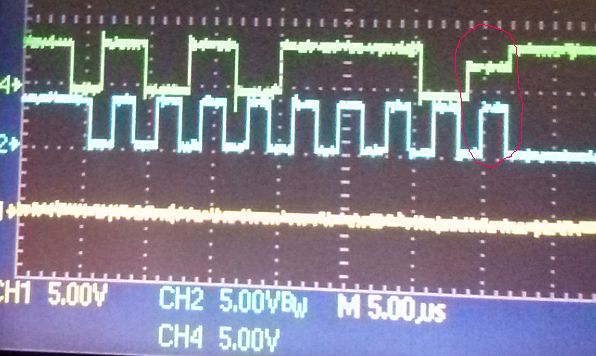

i have an intermediate level when i check ACK bit in an I2C communication ,with uC sending the correct address slave,

It looks like after the 8th bit,the master uC , instead of releasing the SDA line, holds it at high level,in conflict with the acknowledging peripheral

low level , :

Notice that if i use the same pins in GPIO bitbang ,everything works as expected.

I decided to use a MKV31F256VL uController in a prototype needing versatile PWM and good clock speed

I had to communicate via I2C with a RTCC.

I did the same thing in minutes in a previous version using a baseline uC,a MKL15 ,using Code Warrior 10.5,

The PE component for I2C gave me easily the necessary methods.

With this uC i had to use KDS._12C_hal

The GenericI2C component seems not completely implemented for this device.So i tried with a lower level component:fsl_i2C_hal

I used it in a non -OSA project,in a very simple way,not very differently than directly accessing to registers,with no interrupts or semaphores.

I2C_HAL_SetDirMode(I2C0_BASE_PTR,1);

I2C_HAL_SetAddress7bit(I2C0_BASE_PTR,0x6E);

I2C_HAL_SetBaudRate(I2C0_BASE_PTR,60000000,300,0);

I2C_HAL_Enable(I2C0_BASE_PTR);

while(1)

{

Delay_ms(1);

I2C_HAL_SendStart(I2C0_BASE_PTR);

I2C_HAL_WriteByte(I2C0_BASE_PTR,0xAE);

Delay_ms(1);

}

The pullup resistors are both 10K.

Many thanks

Diego

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Solved,for real, this time

it was absolutely my fault,a wrong assumption

there is a bit that i never used and not present in other Freescale uControllers i worked with (KL family), and i was not aware of its existence

is the bit ODE(OpenDrainEnable) in PCR pin configuration register ,missing in the KLfamily,i assumed erroneously that pin configuration was the same after a rapid glance,and that once choosed an alternate I2C function for the pin ,everything would have been in I2C style

And is clearly showed:

Open drain configuration is valid in all digital pin muxing modes

At my weak defense i could say that no mention to this bit in the whole I2C chapter

and the I2C initialization component does not affects this bit(am i right?)

So i could say

not a bug in the uC,compliant to its reference manual

maybe a lack in library,probably inherited from uC with less features,i dare to signal to the support team

As i told it's mainly my fault

Many thanks again for your help ,Daniel

Diego

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanky ou David..

i say solved but the problem was only moved to the next bytes

I changed the device,a well kwn 2402 eeprom,and the problem remains.and i think it is something electrical,not exactly I2C.

In I2C a master,or slave can hold down the SDA or release it to the pullups.

Here there is a kind of electric conflict,it looks the device want to acknowledge,and the master don't release the line.It has no sense to me.

In this moment i have no time at all to go deeper in I2C,that is needed for a secondary feature.

Despite the matter is interesting i have to solve,I would be glad to use quickly some high level component,but it looks that there is no component that can be used easily in a non RTOS project.

I'm here from 7 in the morning,with some rest ,now is 1:22 am,..19 hours more or less

I had to solve or i will drop this project because day are passing by,and this time is not paid at all

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Solved,in some way:

I assumed(and many times this could be misleading if left undiscussed) that the 7-bit address in A1 register was non important,because the first byte i send after start will result as address to my I2C slave,i thought that A1 value was just the uC address ,when uCis in slave mode..

Actually it looks that the value in A1 should be related to the byte sent with I2C_HAL_WriteByte:

If the address of the slave device is 0x57(in bits 7:1) the first data to send using I2C_HAL_WriteByte has to be 0x57 *2=0xAE.

If there is no match the uC marks NACK on the 9th bit.

Shurely, for someone all this sounds natural,but in my primitive acknowledge of I2C,I assumed that the master always puts SDa in Hi-Z at the 9th bit,leaving the slave free to decide wich level put on SDA line.

Can someone explain me how it works in this and other cases?

Many thanks

Diego

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Diego,

I'm not an but have some information that might help you.

MQX-RTOS-Session 11: IC2 Driver|NXP Good video review of I2C.

High overview of I2C: http://www.mcc-us.com/I2CBusTechnicalOverview.pdf

Deeper dive into the I2C protocol: http://www.mcc-us.com/i2cHowToUseIt1995.pdf

Regards,

David