- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: Temperature measurement with ADC

Temperature measurement with ADC

Temperature measurement with ADC

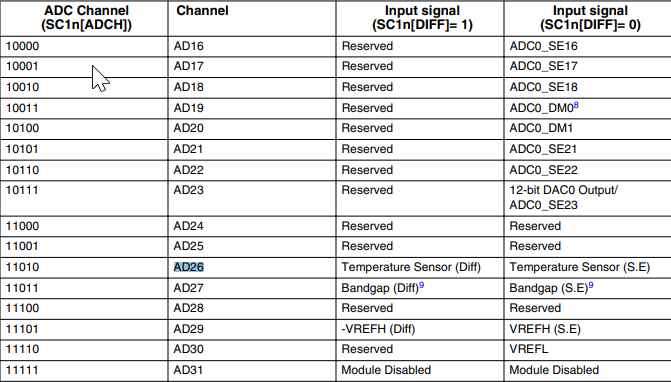

I am using MK61FN1M0VMJ12 microcontroller. I am trying to read it's temperature with built in sensor with ADC CH 26. But I get constant reading of 64875(ADC0_RA) in differential and value 64 when in single ended mode. Same behavior is seen on CH 30. Same piece of code I tested on my K60 Tower Kit and it is working there properly. Can u please tell me what I'm doing wrong. Here is the initialization code:

void init_adc(){

}

void adc0_isr(void){ if (( ADC0_SC1A & ADC_SC1_COCO_MASK ) == ADC_SC1_COCO_MASK) {

} else if (( ADC0_SC1B & ADC_SC1_COCO_MASK ) == ADC_SC1_COCO_MASK) {

}}

Hi prashantdev,

The temperature sensor should be only in the AD26 only and the AD31 mention that disable the module, if you want to do it single ended disable the SC1n[DIFF].

Also, for more information, check the following document that explains how to convert the measurement to temperature.

Let me know if this helps you.

Best Regards,

Alexis Andalon

Thnx Alexis for ur reply.

I'm disabling the channel before calibration. After calibration I've enabled it again.

Thanks for ur effort. Can u tell me if I'm doing something wrong in above posted code ? Because I've tested same code on different K61 microcontroller and behavior is same. Though when I run this code on my K60 tower kit it works. I don't know what I'm doing wrong.

It shows same value (64875) while reading VREFH and VREFL channel. My code works properly on K60N512VMD100 tower kit.