- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: Signal Halt received after setting PEE ext oscilator 50mhz

Signal Halt received after setting PEE ext oscilator 50mhz

hello

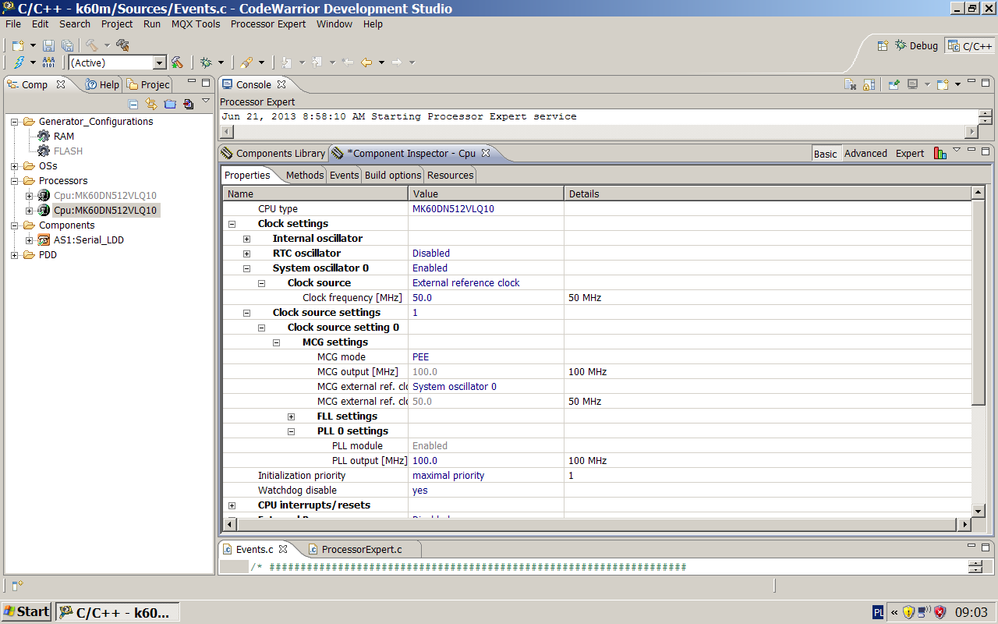

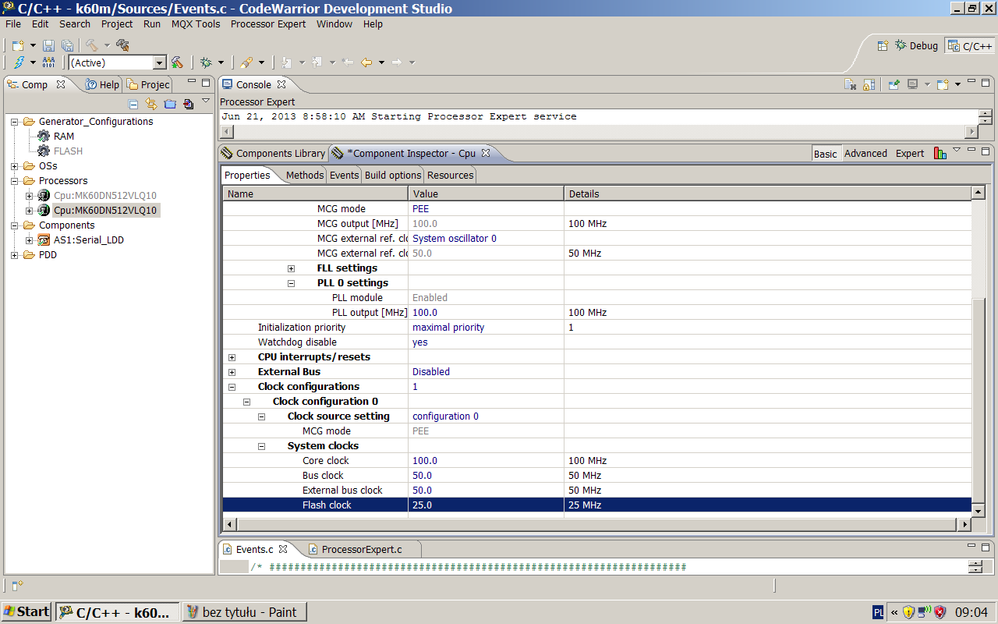

I have problem with my eval board, i setted system oscilator to external reference clock 50mhz and PEE,pll mode with 100mhz core, 50bus, 25mhz flash, and after program, im always getting signal halt received, even if i set to stock clock settings, still getting this error while on secound board, with stock fei mode working fine. i have 50mhz oscilator on eval board, im using Codewarrior, tried to erase with commander, with success, but still error. Any ideas to unlock mcu? and why its bricked?

已解决! 转到解答。

Hi,

From Processor Expert configuration, there could not find any problem.

Please attention that Kinetis 100MHz product with two silicon version, more detailed info please check AN4445:

http://cache.freescale.com/files/32bit/doc/app_note/AN4445.pdf

And please select the correct the chip part number, the part number with "Z" character is Silicon 1.x product.

Could you enter into debug interface with [RAM] or [Flash] target?

And you code run into PE_DEBUGHALT(); before or after enter into main() function.

Thank you for the attention.

Hi Paul,

You could use P&E USB Universal Multilink tool to unsecure the Kinetis chip. When the secured chip doing debug the CodeWarrior software will pop up the mass erase window, you can select [Yes] to unsecure the chip. For the first used chip after manufactory will execute mass erase opertion, which will cause Flash configuration address 0x40C with value 0xFF, this value will be loaded to Flash Security Register and this value set the chip secured. You need to check if 50MHz oscilltor works and you could refer TWR-K60N512 board schematics about related clock circuit design.

http://cache.freescale.com/files/32bit/hardware_tools/schematics/TWR-K60N512-SCH_D.pdf

Wish it helps.

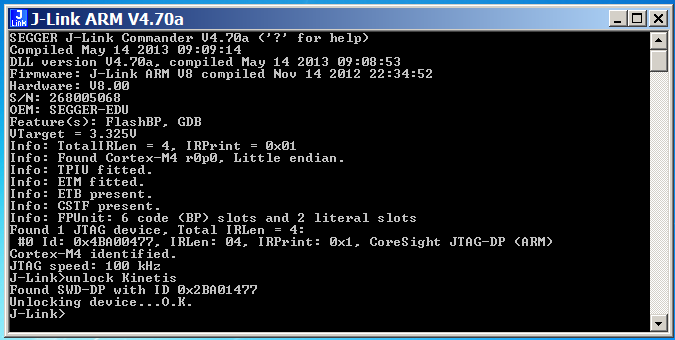

Im using Jlink Edu Segger, one time i saw unsecuring option, i chose to unsecure, i think it did nothing, becouse im still geting the same error, This board is K60 Mini Board from mcuzone.com, i checked that oscilator works, its okay. When i try using jflash arm 4,70 to erase, it looks:

Jlink foun 1jtag device Core id 0x4BA00477 Cortex M4

-reading cfi info

-could not find cfi compilant flash device

-detecting flash memory

-ERROR: Could not find any flash devices

-ERROR: Failed to connect

Still no idea to fix it. This board had demo firmware for present usb mass storage, and it worked.

Hi,

Could you available to check the demo firmware source code (usb mass storage)? It need to make sure the Flash configuratin filed 0x40C with [mass erase is enabled ] setting. Otherwise, it could not use external debugger tool to unsecure the chip. And if it have backdoor application to unsecure the board?

BTW: Segger provides Segger J-Link commander tool, which could use "unlock Kinetis" command to unsecure the Kinetis chip. While the presupposition is [mass erase is enabled] was set.

Thank you for the attention.

Hi,

From Processor Expert configuration, there could not find any problem.

Please attention that Kinetis 100MHz product with two silicon version, more detailed info please check AN4445:

http://cache.freescale.com/files/32bit/doc/app_note/AN4445.pdf

And please select the correct the chip part number, the part number with "Z" character is Silicon 1.x product.

Could you enter into debug interface with [RAM] or [Flash] target?

And you code run into PE_DEBUGHALT(); before or after enter into main() function.

Thank you for the attention.

You have right, i made mistake while using project for MK60DN512VLQ10,while the chip on this board is MK60DN512ZVLQ10 but using that in FEI mode did not make a problem.

I tried both programing Ram and Flash with no difference.

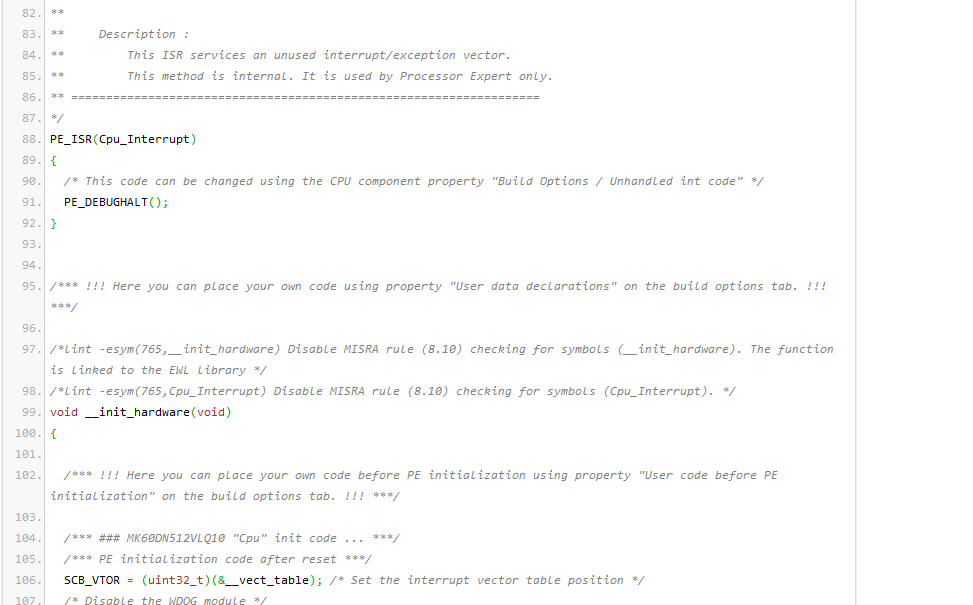

Im always getting Pe_debughalt always at 91line.

http://pastebin.com/0UkDFqXL

Any ideas to revive this board?

Hi Hui Ma

I've already uploaded, take a look on the pastebin link

[C] /* ################################################################### ** T - Pastebin.com

Project is now just empty new bareboard project.

Hi Paul,

I use CodeWarrior MCU V10.4 generate a PEE example project, I test this project works normal for TWR-K60N512 board (both Flash and RAM targets).

If you still meet above problem(enter into pe_debughalt function), I think that was caused by hardware issue.

For your evaluation board could works with FEI mode (chip reset MCG mode), the Kinetis chip should works normally.

I woule suggest you to contact with your evulation board vendor and if they could replace another board.

Wish it helps.

B.R.

Ma Hui

I am having same PE_DEBUGHALT() issue with TWR-K60D100M. I have tried my own and Ma Hui's attached project with same results. It seems that silicon on the Tower board is rev 2.x because it has 2N22D on second line of the physical device (ref: http://cache.freescale.com/files/32bit/doc/app_note/AN4445.pdf). The physical part is PK60DN512VMD10.

I am using CW10.4. and I am trying to get PDB to generate three pulse outs from comparators' outputs (How do I assign PDB Pulse-out signals to physical pins?)

Thanks,

-Irwin

I would like to thanks you all for help, finally i just resolder k60 chip and board just launched.

Now im trying to solve cau issue, i was waiting 2 weeks on service request with no respnse, Using CAU in K60 Chip [CW]

Regards Alex

Hi Alex Paul,

Would you please give us some detailed info about the K60 device? such as part number and mask set on it. We will try to provide a PEE demo based on that and let you try on your board, then might have conclusion for the root cause.

Thanks for your patience!!

B.R

Kan

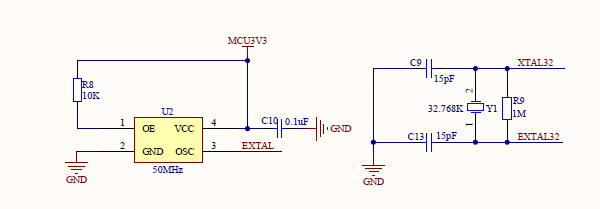

I see the PCB topview, looks no ref clock available, would you please tell us how you connect the 50MHz clock or crystal to the board? a picture should be better.

Thanks for your patience!!

B.R

Kan