- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: Set the frequency of I2C MK10DN512ZVLL10

Set the frequency of I2C MK10DN512ZVLL10

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Set the frequency of I2C MK10DN512ZVLL10

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello everyone,

You can explain how to set the registry I2Cx_F on the management of the frequency in a MK10DN512ZVLL10 (master).

I owe it connected it with a MAC3110 (slave).

How do I choose the different values?

Having only two devices can completely disregard the clock synchronization and arbitration?

Thanks for any help

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello nikivendola:

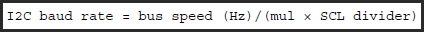

In the I2Cx_F register definition from the Reference Manual you can find the formula to get the I2C baudrate:

bus speed: Depends on your clock configuration (MCG module). For MK10DN512ZVLL10 the default bus clock frequency out of reset is 20.97152 MHz.

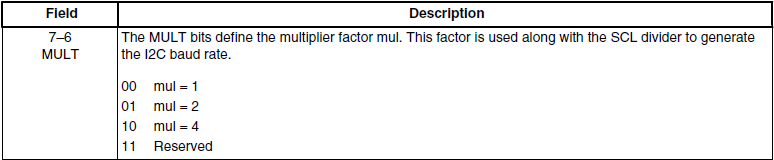

mul: It can be 1, 2 or 4 depending on the setting of the I2Cx_F[MULT] bits (00, 01 or 10):

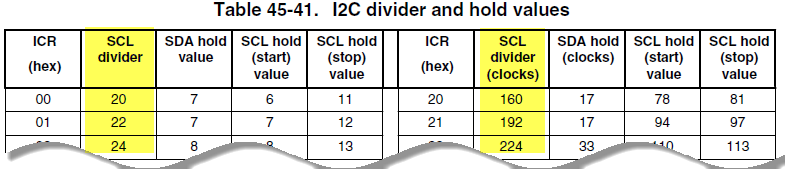

SCL divider: According to I2Cx_F[ICR] (bits 5-0) there is an associated divider value specified in the table I2C divider and hold values:

EXAMPLE:

- To get a 100 kHz I2C bus frequency using the default bus clock frequency you can use the next values:

bus speed = 20.97152 MHz

MULT = 01 -> mul = 2

ICR = 0x16 -> SCL Divider = 104

I2C Baud Rate = 20.97152 MHz / (2 x 104) = 100.824 kHz

- About arbitration and clock synchronization there should not be any issues with only 2 devices (Master and Slave), unless the slave behaves erroneously and pulls the SDA line LOW in a wrong moment.

I hope this helps!

Best Regards!

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello, thank you for your response.

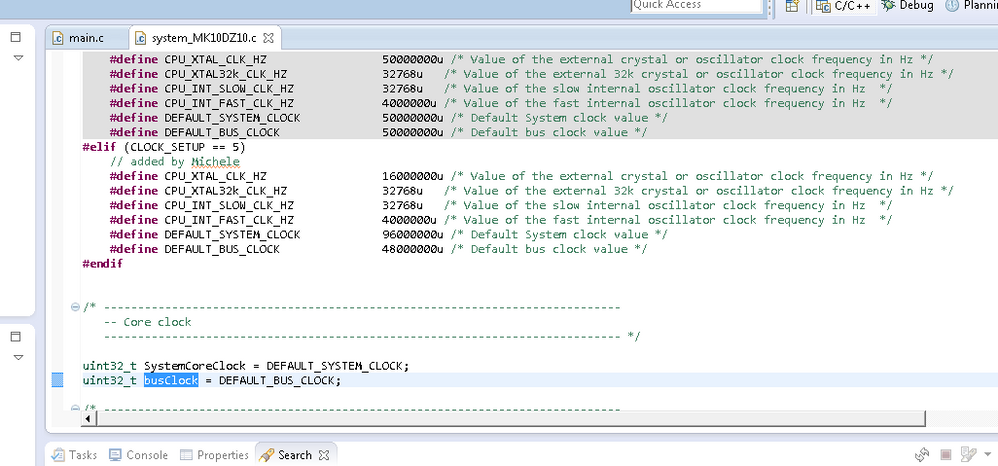

As it is a program that I passed to another person it is possible that this may have set the clock to 48 MHz?

Referring to register I2Cx_SMB

The timeout must be 35 ms (then I have to consider for strength), but the clock to calculate formulas and SHTF1 SHTF2) is always the 48MHz?

SHTF1 I need to figure out who the bus is free while the SHTF2 I note there are problems with the transmission?

Of course also the SLTF dovo set to 1 ...

While for the ACK and the NACK (no CRC):

I have to set the Txak 0 and FACK 1. Any ack I read on RXAK? To read the RXAK I have to check the TCF?

The TCF sets it automatically when the micro after receiving byte or I have to think I?

Rx I 8th bits that end up on 'I2Cx_D, the 9th of ack I read on RXAK?

I can ignore the interrupt to do a broadcast basis?

The busy bit dell'I2Cx_S can I avoid having a single control pocihè master know if tx or receive. However, this field would always written by the micro or I have to set a communication between me and the other?

Best Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello nikivendola:

If the project has an early call to a SystemInit() function and it is using the macros shown in your screenshot (with the macro CLOCK_SETUP defined as 5) as well as the same external crystal (16 MHz) then yes it is likely that the bus clock is 48 MHz.

The way to confirm this is by checking the MCG register configurations. Refer to the MCG Chapter in the Reference Manual. Another option to verify the clock in your device is to use the TRACE_CLKOUT pin as explained by colleague Derek Snell in the next post:

Verifying Internal Clocks in Kinetis

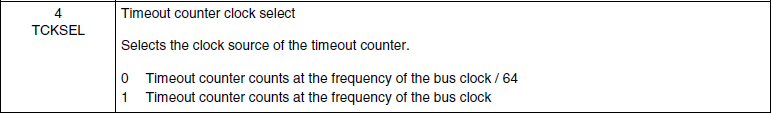

About the SMB timeouts, the frequency used is the one selected by I2Cx_SMB[TCLKSEL]:

The I2Cx_S[BUSY] bit is set or cleared automatically by the I2C module according to the state of the bus.

About the ACK/NACK and the broadcast I am afraid I did not understand your questions.

Best Regards!

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告