- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Re: SAI I2S blocking kl17, EDMA vs DMA

SAI I2S blocking kl17, EDMA vs DMA

SAI I2S blocking kl17, EDMA vs DMA

Hello,

I have a few questions surrounding the attached simple example project transmitting I2S data against an MKL17Z256VFM4. First, is it possible to transmit continuously without delay using a circular ping pong DMA buffer without using 2 DMA channels? Does that require EDMA (not on MKL17)? Why doesn't the __asm("bkpt #0") breakpoint in main ever trigger (why does SAI_DRV_SendDataDma block?)

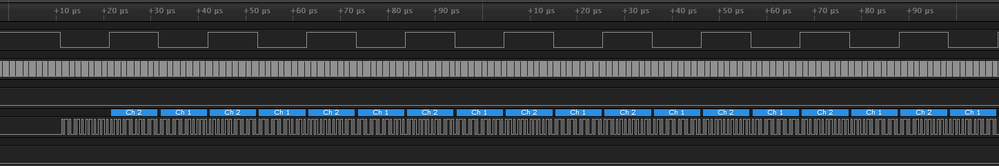

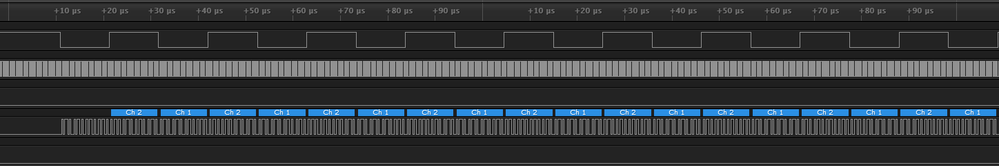

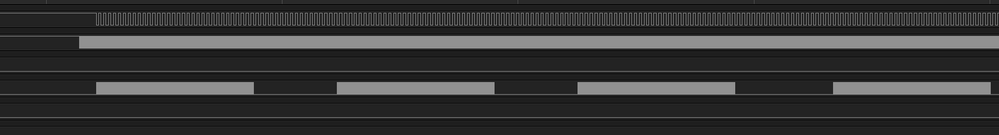

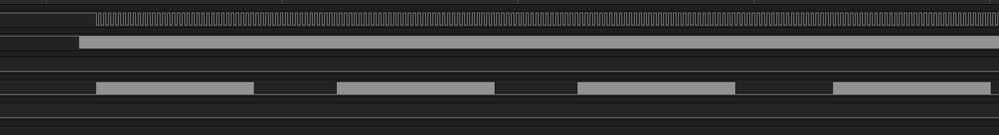

This looks good…

zoomed out - not so good:

It looks like I could create a ping pong buffer using 2 dma channels per RX and 2 channels per TX like the sample code from is there any demo code for using I2S? , but I'm going to need all 4 dma channels on the MKL17 for my application (1 for SAI/I2S tx, 1 for SAI/I2S rx, 1 for FlexIO/TDM tx, 1 for FlexIO/TDM rx).

Edit: To clarify my application, I need to:

- Implement a 4-channel TDM driver using FlexIO

- Forward 2 (L,R) incoming I2S channels to outgoing TDM

- Forward 3 (L, R, Mic) incoming TDM channels to two outgoing I2S channels (one SAI, one FlexIO)

- No processing, just conversion between digital audio standards

I'm interested in the viability of this on an MKL17.

Thanks,

Jake Jennings

Original Attachment has been moved to: test-sai-i2s-dma.zip

To achieve 2x i2s TX, 1x i2s RX, TDM4 TX and TDM4 RX on one chip, I have drawn the following conclusions:

- Most chips have 1 SAI module which supports only 2 channels L/R, 1x RX, 1x TX

- Higher end chips have SAI module that supports left-aligned TDM, but still 1x RX 1x TX

- With basic DMA, for continuous conversion, you must use 2 channels to make a ping-pong buffer

- With enhanced eDMA, you can set up ping-pong buffers with a single eDMA channel

- FlexIO could be used for i2s, but chips with one SAI module AND FlexIO all only have 4 channels of basic DMA (not eDMA) except K8x

- 4 is not enough DMA channels for continuous conversion

- K8x is the only option for this application

Unfortunately, going from a KL17 to a K8x chip is a serious cost increase. Any advice or corrections are welcome.

Thanks,

Jake

'K' series parts (even K10) have an SAI with more capable bus modes including MANY analog channels per RX/TX pair in a TDM or AC97 mode. The DMA to such a channel can be configured to do ALL channel (de-)interleave and double-buffering. For reference, see also:

is there any demo code for using I2S?

BUT unfortunately in that post, my code was made for the 'Ver 1' ('Z') silicon, and the I2S/SAI changed significantly going into V2 silicon, so the setup of that interface is NOT going to directly apply to current devices...

The TDM support in K series is nice, but I need to run 2X TDM and 3X I2S (1 rx 2 tx) simultaneously which does not seem possible until K8x

The ADAU1761 DSP I am using only has one set of digital TX/RX, which is why I wanted to do I2S <-> TDM4 conversions to interface with several I2S-only components. I think it will be better to switch to the TI C5000 series DSP instead of using the main MCU as a converter.

My mistake: Although most K series have 1 SAI module, some of them support multiple RX/TX lines while sharing clock lines, such as K24, K64