- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Question about recovery time from VLPS mode (or stop mode when PLL is stopped) - K and KL parts

Question about recovery time from VLPS mode (or stop mode when PLL is stopped) - K and KL parts

Hi All

Comparing normal STOP mode and very low power STOP mode it is possible to reduce current consumption by a factor of 10..100.

In normal STOP mode the PLL can however (optionally) continue to run and so there is no recovery time after returning to RUN mode (waiting for the PLL to lock again).

In VLPS mode the PLL is always stopped (the MCG is set back to PEE mode) so the first thing that needs to be done (when not running without PLL) is to reconfigure and wait for it to lock again so that the clock frequencies are correct again.

I am wondering about the effect of this when being woked by peripherals - like UART - where the baud rate is not correct during this period. Is the recommendation to avoid using the PLL in such cases or can this procedure be kept short enough that no disruption actually takes place?

Regards

Mark

已解决! 转到解答。

Hi,

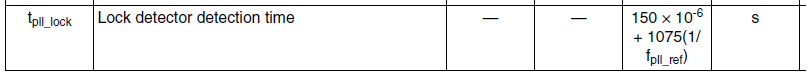

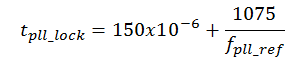

I agree with the conditions you are suggesting, since the PLL has a Lock time and to operate peripheral using the PLL as the source clock for them will be dependent to the Lock detection time. This Lock detection time is dependent to the PLL reference frequency range and according to the reference manual it is:

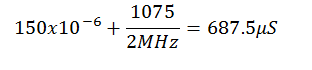

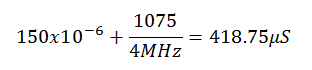

The fpll_ref is the PLL reference frequency range and it can be min. 2.0 MHz and max. 4MHz; with this we can calculate the range of the Lock detection time that will be:

at 2 MHz:

at 4 MHz:

If the purpose is to optimize our application then we see that the lock detection time is quite high and the suggested conditions by Mark are suitable for this.

Best Regards,

Adrian

Hi All

After doing some additional work and measuring the PLL recovery time to be around 400us I decided that the best strategy is to not use the PLL, thus avoiding the peripheral operating at an incorrect speed until the final frequency becomes available (and also to avoid possible receive overruns during that time).

Possibly, if the system speed needs to be higher, some peripheral clock settings could be dynamically changed to suit the intermediate clock, an interrupt enabled when the PLL has locked, and the system allowed to run at the intermediate speed. The PLL interrupt could then dynamically change all peripherals clock settings again and continue but there may be peripherals that need to be stopped to change clock settings so this may not be workable generally.

Regards

Mark

Hi,

I agree with the conditions you are suggesting, since the PLL has a Lock time and to operate peripheral using the PLL as the source clock for them will be dependent to the Lock detection time. This Lock detection time is dependent to the PLL reference frequency range and according to the reference manual it is:

The fpll_ref is the PLL reference frequency range and it can be min. 2.0 MHz and max. 4MHz; with this we can calculate the range of the Lock detection time that will be:

at 2 MHz:

at 4 MHz:

If the purpose is to optimize our application then we see that the lock detection time is quite high and the suggested conditions by Mark are suitable for this.

Best Regards,

Adrian