- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Minimum register settings for USBPHY

Minimum register settings for USBPHY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Minimum register settings for USBPHY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

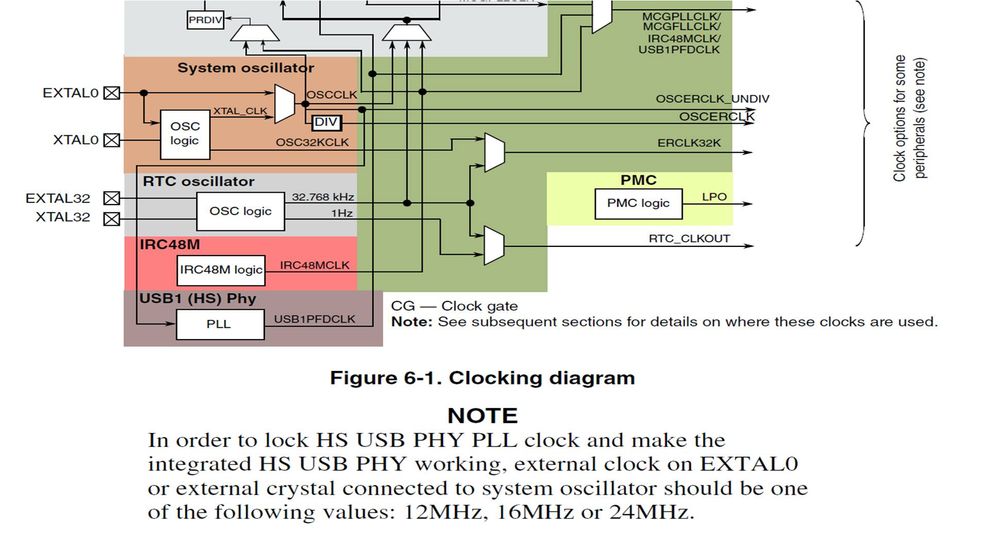

What are the minimum register settings to get the USBHS PHY PLL to lock? We have a very clean 12MHz clock going into the PLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sam,

just to corroborate, do you want to know the specific clock configuration (MCG) to supply clock signal needed on USB to work in High Speed mode?

Regards,

Isaac

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe we have our MCG set correctly. I am following the updated reference manual information from section 55.3.2 which indicates what registers need to be touched. I think there is one setting missing to enable the trim:

TRIM_DIV_SEL_OVERRIDE - Override enable for PLL_DIV_SEL, when set, the register value in USBPHY_PLL_SIC[1:0] will be used.

The PLL is still not locking.

Is there a favored frequency for that PLL (12 MHz vs 24 MHz)? I expect to be giving it a clock (square wave) rather than a 12 MHz sine wave. Is that correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Could you please provide me information about your used MCU (or development board such as TWR, FRDM) and i would look for best configuration on it.

Thanks,

Isaac Avila

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are using the K65:

https://cache.freescale.com/files/32bit/doc/ref_manual/K65P169M180SF5RMV2.pdf

We have a 12MHz external oscillator on EXTAL (no crystal). We have VBUS0 and VBUS1 sorted together and tied to 5V.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sam,

According to K65 Reference Manual and in response to

is there a favored frequency for that PLL (12 MHz vs 24 MHz)? I expect to be giving it a clock (square wave) rather than a 12 MHz sine wave. Is that correct?

PLL's input clock should be 12, 16 or 24 Mhz so there is no favored frequency (12 or 24MHz) due you can use either 12, 16 or 24 MHz, and this clock signal should be a square wave rather than a sine one.

Besides, TRIM_DIV_SEL_OVERRIDE bit (bit 0 from USBPHY_TRIM_OVERRIDE_EN register) should be enabled in order to use PLL_DIV_SEL values (24, 16 or 12 Mhz).

Could you please send me your code for looking any missing configuration?

Regards,

Isaac Avila

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We never make it to the printf statement.

void main_task(os_task_param_t task_init_data) { /* Write your local variable definition here */ /* Initialization of Processor Expert components (when some RTOS is active). DON'T REMOVE THIS CODE!!! */ #ifdef MainTask_PEX_RTOS_COMPONENTS_INIT PEX_components_init(); #endif /* End of Processor Expert components initialization. */

#ifdef PEX_USE_RTOS while (1) { #endif

/* Write your code here ... */ _int_install_unexpected_isr(); BOARD_ClockInit(); dbg_uart_init(); GPIO_DRV_Init(gInputPins, gOutputPins);

*(volatile uint8_t*)(0x40064000) |= MCG_C1_IRCLKEN_MASK; //32kHz IRC enable *(volatile uint8_t*)(0x40065000) |= OSC_CR_ERCLKEN_MASK; //external reference clock enable *(volatile uint32_t*)(0x40048004) |= SIM_SOPT2_USBREGEN_MASK; //enable USB PHY PLL regulator *(volatile uint32_t*)(0x40048030) |= SIM_SCGC3_USBHSPHY_MASK; //open USB PHY clock gate *(volatile uint32_t*)(0x40047008) &= ~USBPHY_CTRL_SFTRST_MASK; //release PHY from reset *(volatile uint32_t*)(0x40047008) &= ~USBPHY_CTRL_CLKGATE_MASK; *(volatile uint32_t*)(0x400A2130) |= 0x1; // set trim // *(volatile uint32_t*)(0x40047008) &= 0xFF8FFFFF; // *(volatile uint32_t*)(0x40047008) |= 0x00100000; // USBPHY_CTRL &= 0xFF8FFFFF; // USBPHY_CTRL |= 0x00100000; //Clear to 0 to run clocks

//power up PLL int crystal_val = g_xtal0ClkFreq; if(crystal_val == 24000000) USBPHY_PLL_SIC |= USBPHY_PLL_SIC_PLL_DIV_SEL(0); else if(crystal_val == 16000000) USBPHY_PLL_SIC |= USBPHY_PLL_SIC_PLL_DIV_SEL(1); else if(crystal_val == 12000000) *(volatile uint32_t*)(0x400A20A0) |= USBPHY_PLL_SIC_PLL_DIV_SEL(2);

// *(volatile uint32_t*)(0x400A20A0) |= USBPHY_PLL_SIC_PLL_POWER_MASK; *(volatile uint32_t*)(0x400A20A0) &= ~0x00010000; // disable bypass *(volatile uint32_t*)(0x400A20A0) &= ~0x00002000; // disable pll output *(volatile uint32_t*)(0x400A20A0) |= 0x01003; int locked = *(volatile uint32_t*)(0x400A20A0) & USBPHY_PLL_SIC_PLL_LOCK_MASK; while (locked == 0) { locked = *(volatile uint32_t*)(0x400A20A0) & USBPHY_PLL_SIC_PLL_LOCK_MASK; _time_delay_ticks(500); } printf("pll locked\n");

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sam,

I already could test your code and effectively, it works doing modifications that I mentioned before.

Here it is the code that I use to test

MCG_C1 |= MCG_C1_IRCLKEN_MASK; /* 32kHz IRC enable */

OSC_CR |= OSC_CR_ERCLKEN_MASK; /* External reference clock enable */

SIM_SOPT2 |= SIM_SOPT2_USBREGEN_MASK; /* Enable USB PHY PLL regulator */

SIM_SCGC3 |= SIM_SCGC3_USBHSPHY_MASK; /* Open USB PHY clock gate */

SIM_USBPHYCTL = SIM_USBPHYCTL_USB3VOUTTRG(6); /* trim the USB regulator output to be 3.13V */

SIM_USBPHYCTL |= SIM_USBPHYCTL_USBVREGSEL_MASK; /* Selects VREG_IN1 */

USBPHY_CTRL &= ~USBPHY_CTRL_SFTRST_MASK; /* Release PHY from reset */

USBPHY_CTRL &= ~USBPHY_CTRL_CLKGATE_MASK; /* Gate UTMI Clocks */

/* Enables TRIM OVERRIDE */

USBPHY_TRIM_OVERRIDE_EN |= USBPHY_TRIM_OVERRIDE_EN_CLR_TRIM_DIV_SEL_OVERRIDE_MASK;

/* Power PHY's PLL */

USBPHY_PLL_SIC |= USBPHY_PLL_SIC_CLR_PLL_POWER_MASK;

/* In TWR-K65F180M board, Crystal is 16 MHz */

int crystal_val = 16000000;

/* Select appropiate value for PLL_DIV_SEL */

if(crystal_val == 24000000)

USBPHY_PLL_SIC &= ~USBPHY_PLL_SIC_PLL_DIV_SEL_MASK;

else if(crystal_val == 16000000)

USBPHY_PLL_SIC |= USBPHY_PLL_SIC_PLL_DIV_SEL(1);

else if(crystal_val == 12000000)

USBPHY_PLL_SIC |= USBPHY_PLL_SIC_PLL_DIV_SEL(2);

/* Wait until PLL is locked */

while (!(USBPHY_PLL_SIC & USBPHY_PLL_SIC_PLL_LOCK_MASK));

/* if program reaches this point, PLL was locked successfully */

i++;

In my hardware settings, I connected VBUS from USB connector to VREG_IN1. I used TWR-K65F180M so you could check its schematic for any doubt about hardware connections.

I hope this could help,

Regards,

Isaac Avila

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

This was most certainly helpful; however, the key that made it work for us was stating that our bench oscillator clock was actually a crystal. We have not been able to get the USBPHY PLL to lock without telling the K65 that the clock source is a crystal (the demo board uses a crystal).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sam,

As you may know, design team confirmed this is a silicon issue, and they will create an errata for this.

As a workaround to your problem, maybe you need to pretend what connected is a crystal and that can make HS USB PHY to work.

Best Regards,

Isaac

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sam

It is good to know this feedback.

cutworth is working on this issue as he had told you on K65 ES Part USB1 PHY PLL Not Locking.

Hope this could be solve soon.

Best Regards,

Isaac

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Sam,

Doing a quick review to your code, I think there is a mistake on lines 23 and 25, you are pointing to direction 0x40047008 which is mapped to SIM_USBPHYCTL (Where USB Regulator is configured) instead of pointing to direction 0x400A2030 which is mapped to USBPHY_CTRL register (where you should clear USBPHY_CTRL_CLKGATE_MASK and USBPHY_CTRL_SFTRST_MASK).

Could you please validate this?

As soon as i can get a K65 Board, I will test your code using these modifications,

Best Regards,

Isaac