- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- Re: MK66 SDRAM databus lost

MK66 SDRAM databus lost

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi I`m thinking of using the MK66FN2M0VLQ18 in a project and need to add SDRAM but I`m a bit confused as I cannot find any examples. It seems that Databus 0 - 15 is not available on FB_AD0-15 as it is used for the address lines - Do I need to use latches to multiplex the data bus with the address lines?

Any help would be greatly appreciated

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have checked the data sheet of MT48LC8M16A2 – 2 Meg x 16 x 4 Banks, this is the parameters:

row addressing:4K A[11:0]

column addressing:512 A[8:0]

bank addressing:4 BA[1:0]

You have to use the Table 35-8. SDRAM Controller to SDRAM Interface (16-Bit Port, 9-Column Address Lines) in RM of K66, the data bus is hooked to the High half word, I think your connection is okay. but I do not check the pin assignment.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Great Thanks Xiangjun

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Daniel,

Regarding your question, i am a bit confused, do you interface with SDRAM or SRAM? if you hook SDRAM, you have to use SDRAM SDR controller to connect, if you use SRAM/Nor flash, you can use FlexBus to connect.

If you use SDRAM, pls refer to the follwoing table in reference manual of K66.

Pls tell us the device even part number you want to hook.

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi XiangJun

Thanks for your reply.

The SDRAM is MT48LC8M16A2P-75 (2 Meg x 16 x 4 Banks) - I have attached the pin mapping to what I think may work?

| MK66 Pin (LQFP) | MK66 Pin Name | MK66 mode | MT48LC8M16A2P pin | MT48LC8M16A2P pin NAME | |

| 81 | PTB0 | SDRAM_CAS_b | 17 | SDRAM_CAS | |

| 82 | PTB1 | SDRAM_RAS_b | 18 | SDRAM_RAS | |

| 83 | PTB2 | SDRAM_WE | 16 | SDRAM_WE | |

| 84 | PTB3 | SDRAM_CS0_b | 19 | SDRAM_CS0 | |

| 106 | PTC3 | CLKOUT | 38 | SDRAM_CLOCKOUT | |

| 125 | PTC18 | SDRAM_DQM1 | 39 | SDRAM_DQM1 | |

| 126 | PTC19 | SDRAM_DQM0 | 15 | SDRAM_DQM0 | |

| 136 | PTD7 | SDRAM_CKE | 37 | SDRAM_CKE | |

| 96 | PTB17 | FB_AD16/ SDRAM_D16 | 2 | SDRAM_D0 | |

| 95 | PTB16 | FB_AD17/ SDRAM_D17 | 4 | SDRAM_D1 | |

| 92 | PTB11 | FB_AD18/ SDRAM_D18 | 5 | SDRAM_D2 | |

| 91 | PTB10 | FB_AD19/ SDRAM_D19 | 7 | SDRAM_D3 | |

| 90 | PTB9 | FB_AD20/ SDRAM_D20 | 8 | SDRAM_D4 | |

| 89 | PTB8 | FB_AD21/ SDRAM_D21 | 10 | SDRAM_D5 | |

| 88 | PTB7 | FB_AD22/ SDRAM_D22 | 11 | SDRAM_D6 | |

| 87 | PTB6 | FB_AD23/ SDRAM_D23 | 13 | SDRAM_D7 | |

| 120 | PTC15 | FB_AD24/ SDRAM_D24 | 42 | SDRAM_D8 | |

| 119 | PTC14 | FB_AD25/ SDRAM_D25 | 44 | SDRAM_D9 | |

| 118 | PTC13 | FB_AD26/ SDRAM_D26 | 45 | SDRAM_D10 | |

| 117 | PTC12 | FB_AD27/ SDRAM_D27 | 47 | SDRAM_D11 | |

| 102 | PTB23 | FB_AD28/ SDRAM_D28 | 48 | SDRAM_D12 | |

| 101 | PTB22 | FB_AD29/ SDRAM_D29 | 50 | SDRAM_D13 | |

| 100 | PTB21 | FB_AD30/ SDRAM_D30 | 51 | SDRAM_D14 | |

| 99 | PTB20 | FB_AD31/ SDRAM_D31 | 53 | SDRAM_D15 | |

| 132 | PTD5 | FB_AD1/ SDRAM_A9 | 32 | A7 | |

| 131 | PTD4 | FB_AD2/ SDRAM_A10 | 31 | A6 | |

| 130 | PTD3 | FB_AD3/ SDRAM_A11 | 30 | A5 | |

| 129 | PTD2 | FB_AD4/ SDRAM_A12 | 29 | A4 | |

| 115 | PTC10 | FB_AD5/ SDRAM_A13 | 26 | A3 | |

| 114 | PTC9 | FB_AD6/ SDRAM_A14 | 25 | A2 | |

| 113 | PTC8 | FB_AD7/ SDRAM_A15 | 24 | A1 | |

| 112 | PTC7 | FB_AD8/ SDRAM_A16 | 23 | A0 | |

| 110 | PTC5 | FB_AD10/ SDRAM_A18 | 33 | A8 | |

| 109 | PTC4 | FB_AD11/ SDRAM_A19 | 34 | A9 | |

| 105 | PTC2 | FB_AD12/ SDRAM_A20 | 22 | A10 | |

| 104 | PTC1 | FB_AD13/ SDRAM_A21 | 35 | A11 | |

| 103 | PTC0 | FB_AD14/ SDRAM_A22 | 20 | BANK SEL 0 | |

| 97 | PTB18 | FB_AD15/ SDRAM_A23 | 21 | BANK SEL 1 |

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

When using 16-bit wide SDRAM and D16-D31 on the MCU (mandatory from what I understand), is this realy correct:

| 125 | PTC18 | SDRAM_DQM1 | 39 | SDRAM_DQM1 | |

| 126 | PTC19 | SDRAM_DQM0 | 15 | SDRAM_DQM0 |

I thought one should connect MCU DQM3 and DQM2 to SDRAM DQM1 and DQM0, or?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Yes I`m pretty sure its correct, I have to admit the datasheet is pretty poor at explaining how to wire SDRAM but the tables 35-4 to 13 are correct so you can blindly follow them. We invited a NXP technical expert to our business to double check for us and he confirmed that the above wiring is correct. The Prototype boards are being made next week so I`ll be pretty disappointed if they don`t work.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

I am working with K65, but the Reference manual looks the same. We are about to order a board any day. What I have been looking at is "Figure 35-2. Connections for External Memory Port Sizes" and from that figure my conclusion is that BS3 and BS2 shall be used with 16-bit wide memory (BS[3:0] is the DQM, see table 35-2). You can also check this thread on the same topic: https://community.nxp.com/thread/437787

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi

I am so confused - I think you are right BS3 and BS2 should be used with 16bit SDRAM but as it is memory mapped does it matter?

Bank select and DQM are two separate items.

Synchronous dynamic random-access memory - Wikipedia

- DQM Data Mask. (The letter Q appears because, following digital logic conventions, the data lines are known as "DQ" lines.) When high, these signals suppress data I/O. When accompanying write data, the data is not actually written to the DRAM. When asserted high two cycles before a read cycle, the read data is not output from the chip. There is one DQM line per 8 bits on a x16 memory chip or DIMM.

Bank Selection (BAn)[edit]

SDRAM devices are internally divided into either 2, 4 or 8 independent internal data banks. One to three Bank Address inputs (BA0, BA1 and BA2) are used to select which bank a command is directed toward.

I`m pretty sure that you can wire the bank select lines straight to the next available address lines.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

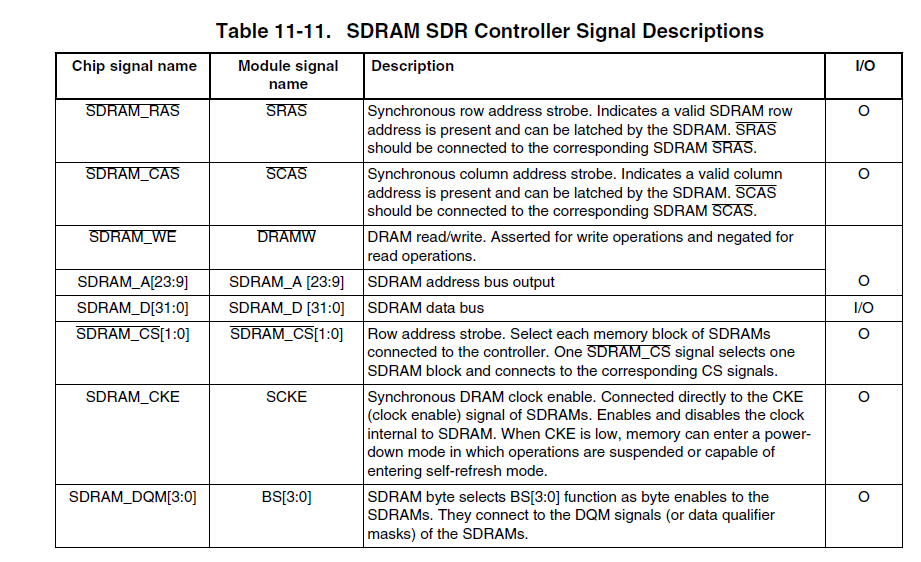

When checking table 35-2 BS[3:0] should be interpret as "Byte Select" and not "Bank Selection":

"SDRAM byte selects BS[3:0] function as byte enables to the SDRAMs. They connect to the DQM signals (or data qualifier masks) of the SDRAMs.".

In Figure 35-2 the BS signals have the text "Byte Enable" to the left of them to make it more confusing.

A problem is that NXP uses BS instead of DQM in the Reference manual and DQM in the Datasheet not BS.

I am still not 100% sure what is right, but I whould really like be 100% sure before we order our board...

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is ridiculous - why is the datasheet so confusing?

I am going to contact NXP directly and get them to advise, once done I will let you know on this post.

Best Regards Dan.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi I have contact NXP and they kindly reviewed the design for me, it looks like the design was wrong and that the DQM signals need to connect to DQM2 and DQM3.

Also just to clarify the Bank address lines are correct:

In terms of the Bank Address lines, on the SDR these select one of the 4 internal banks. To make the memory space mapped to the K66 contiguous, we use the next 2 address lines. So I’m happy with using SDRAM_A22 and SDRAM_A23 connected to BANK_SEL0 and BANK_SEL1. That is consistent with both the TWR schematic and the Table 35-16 example in the device reference manual (pdf page 900) of Rev2 reference manual.

So with reasonable confidence below is how you connect 128Mbit of SDRAM to the MK66 in 16bit mode, although we will only 100% know once we have re-spun the PCB.

Connecting MT48LC8M16A2P to MK66FN2M0VLQ18.

| MK66 Pin (LQFP) | MK66 Pin Name | MK66 mode | MT48LC8M16A2P pin | MT48LC8M16A2P pin NAME | |

| 81 | PTB0 | SDRAM_CAS_b | 17 | SDRAM_CAS | |

| 82 | PTB1 | SDRAM_RAS_b | 18 | SDRAM_RAS | |

| 83 | PTB2 | SDRAM_WE | 16 | SDRAM_WE | |

| 84 | PTB3 | SDRAM_CS0_b | 19 | SDRAM_CS0 | |

| 106 | PTC3 | CLKOUT | 38 | SDRAM_CLOCKOUT | |

| 124 | PTC17 | SDRAM_DQM3 | 39 | SDRAM_DQMU | |

| 123 | PTC16 | SDRAM_DQM2 | 15 | SDRAM_DQML | |

| 136 | PTD7 | SDRAM_CKE | 37 | SDRAM_CKE | |

| 96 | PTB17 | FB_AD16/ SDRAM_D16 | 2 | SDRAM_D0 | |

| 95 | PTB16 | FB_AD17/ SDRAM_D17 | 4 | SDRAM_D1 | |

| 92 | PTB11 | FB_AD18/ SDRAM_D18 | 5 | SDRAM_D2 | |

| 91 | PTB10 | FB_AD19/ SDRAM_D19 | 7 | SDRAM_D3 | |

| 90 | PTB9 | FB_AD20/ SDRAM_D20 | 8 | SDRAM_D4 | |

| 89 | PTB8 | FB_AD21/ SDRAM_D21 | 10 | SDRAM_D5 | |

| 88 | PTB7 | FB_AD22/ SDRAM_D22 | 11 | SDRAM_D6 | |

| 87 | PTB6 | FB_AD23/ SDRAM_D23 | 13 | SDRAM_D7 | |

| 120 | PTC15 | FB_AD24/ SDRAM_D24 | 42 | SDRAM_D8 | |

| 119 | PTC14 | FB_AD25/ SDRAM_D25 | 44 | SDRAM_D9 | |

| 118 | PTC13 | FB_AD26/ SDRAM_D26 | 45 | SDRAM_D10 | |

| 117 | PTC12 | FB_AD27/ SDRAM_D27 | 47 | SDRAM_D11 | |

| 102 | PTB23 | FB_AD28/ SDRAM_D28 | 48 | SDRAM_D12 | |

| 101 | PTB22 | FB_AD29/ SDRAM_D29 | 50 | SDRAM_D13 | |

| 100 | PTB21 | FB_AD30/ SDRAM_D30 | 51 | SDRAM_D14 | |

| 99 | PTB20 | FB_AD31/ SDRAM_D31 | 53 | SDRAM_D15 | |

| 132 | PTD5 | FB_AD1/ SDRAM_A9 | 32 | A7 | |

| 131 | PTD4 | FB_AD2/ SDRAM_A10 | 31 | A6 | |

| 130 | PTD3 | FB_AD3/ SDRAM_A11 | 30 | A5 | |

| 129 | PTD2 | FB_AD4/ SDRAM_A12 | 29 | A4 | |

| 115 | PTC10 | FB_AD5/ SDRAM_A13 | 26 | A3 | |

| 114 | PTC9 | FB_AD6/ SDRAM_A14 | 25 | A2 | |

| 113 | PTC8 | FB_AD7/ SDRAM_A15 | 24 | A1 | |

| 112 | PTC7 | FB_AD8/ SDRAM_A16 | 23 | A0 | |

| 110 | PTC5 | FB_AD10/ SDRAM_A18 | 33 | A8 | |

| 109 | PTC4 | FB_AD11/ SDRAM_A19 | 34 | A9 | |

| 105 | PTC2 | FB_AD12/ SDRAM_A20 | 22 | A10 | |

| 104 | PTC1 | FB_AD13/ SDRAM_A21 | 35 | A11 | |

| 103 | PTC0 | FB_AD14/ SDRAM_A22 | 20 | BANK SEL 0 | |

| 97 | PTB18 | FB_AD15/ SDRAM_A23 | 21 | BANK SEL 1 |

Regards Dan.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

Any update to how the above pinout worked?

Thanks,

Ryan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I have checked the data sheet of MT48LC8M16A2 – 2 Meg x 16 x 4 Banks, this is the parameters:

row addressing:4K A[11:0]

column addressing:512 A[8:0]

bank addressing:4 BA[1:0]

You have to use the Table 35-8. SDRAM Controller to SDRAM Interface (16-Bit Port, 9-Column Address Lines) in RM of K66, the data bus is hooked to the High half word, I think your connection is okay. but I do not check the pin assignment.

BR

Xiangjun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks Xiangjun

Just one more clarification:

Do I wire the bank select lines to the upper address lines?

i.e.

BANK_SEL_0 = SDRAM_A22

BANK_SEL_1 = SDRAM_A23

Best Regards Dan.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

For K66, you can locate the SDRAM to the address space:

0x8000_0000–0x8FFF_FFFF SDRAM (External RAM - Write-through) All masters

in other words, your SRDAM space will be:

0x8000 0000 to 0x80FF FFFF for MT48LC8M16A2

But you have to initialize the SDRAM controller before you access the SDRAM.

I attach an doc, hope it can help you.

BR

XiangJun Rong