- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Kinetis K65 with SDRAM 512Mb

Kinetis K65 with SDRAM 512Mb

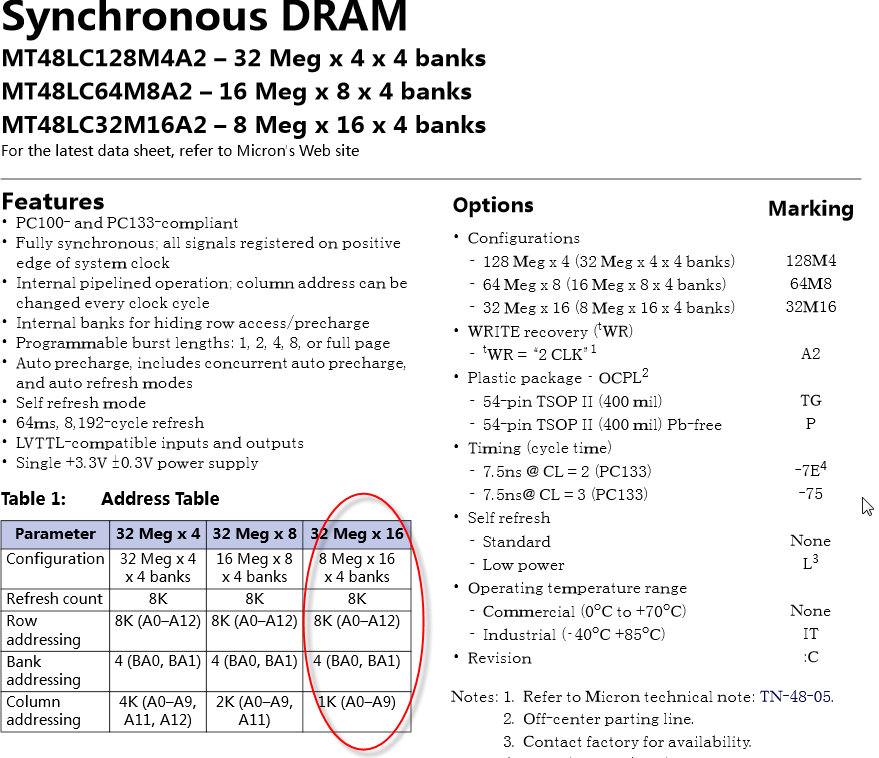

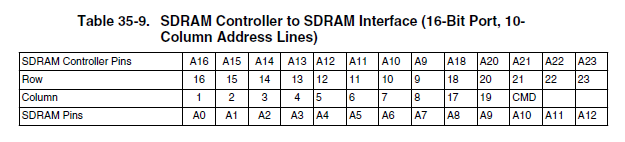

Is it possible to connect the MCU MK65 to SDRAM MT48LC64M8A2? SDRAM has 8192 rows by 2048 columns, 10 columns A[9:0] SDRAM can be connected to A[16:9], A[22:20], A18 of MK65FN2M0VMI18, which is described in table 35-9 K65P169M180SF5RMV2.pdf. But on the page 890 is "The maximum SDRAM address size is 128 Mbits" and I want to connect SDRAM 512Mbit (64MB). Isn't this limit determined only for FlexBus and SDRAM can exceed this limit?

已解决! 转到解答。

Hi Jiri Dohnal,

I checked the data sheet of MT48LC64M8A2, and looks like you are going to use the following configuration in red circle with table 35-9 , right?

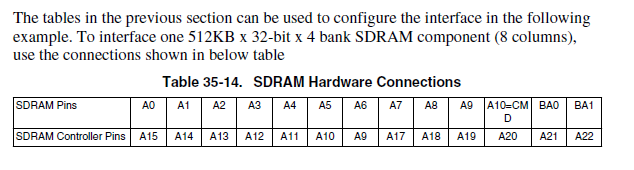

If yes, I think maybe you have ignored the BA0 and BA1, which should be also listed as two of the address lines, such as table 35-14

so if you connected in the way of table 35-9 shown, only 128Mbit can be accessed with predefined states on BA0 and BA1, it is not a limitation for flexbus, but for SDRAM mapping.

Hope that makes sense,

Please kindly let me know if you have any issue.

Have a great day,

Kan

NXP Technical Support

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Jiri Dohnal,

I checked the data sheet of MT48LC64M8A2, and looks like you are going to use the following configuration in red circle with table 35-9 , right?

If yes, I think maybe you have ignored the BA0 and BA1, which should be also listed as two of the address lines, such as table 35-14

so if you connected in the way of table 35-9 shown, only 128Mbit can be accessed with predefined states on BA0 and BA1, it is not a limitation for flexbus, but for SDRAM mapping.

Hope that makes sense,

Please kindly let me know if you have any issue.

Have a great day,

Kan

NXP Technical Support

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Kan_Li,

you're right, I forgot that bank adresses BA0, BA1 should have been connected to GPIOs and switch banks manually.

Can I ask you how to connect more then one SDRAM to K65/K66? On an older versions of Kinetis (K60, K61), this limitation was only 1Gb. Now on newer and faster Kinetis I can connect 2 SDRAM (diferentiated by SDRAM_CS0, SDRAM_CS1), every with 128Mbit limitation?

Thank you very much for your answer.

Jiri Dohnal