- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Kinetis K60 ADC performance + histogram tool

Kinetis K60 ADC performance + histogram tool

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Kinetis K60 ADC performance + histogram tool

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've got some concerns about the performance of the 16-bit Kinetis ADC. To help address those, I've made some major mods to the IAR/Freescale ADC demo to generate histograms of ADC readings. Not good news, at least using the K60 Tower kit board reading the onboard pot. Granted, the board does not have a nice stable Vref and pot voltage, but I'm seeing between 4 and 5 bits of noise in averaged readings. If I interpret the data sheet correctly, this ain't meeting spec... Anyone have a genuine product design that does substantially better than this?

If anyone cares to compare results, I've attached the code and sample histograms in the adc_histo\histograms\ folder.

Original Attachment has been moved to: adc_histo.zip

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Software

There are several configurations application depended; these are some recommendations that will improve the ADC performance

- SAR ADC calibration

- Higher supply VREFH means larger LSB with more stable results

- Slower system-core clock rates to minimize periodic noise. If the application allows it you can sample at VLPR

- Lower ADC clock rates to allow more time for sampling and settling of comparator

- Ambient, cold temperatures better than hot for thermal noise

- Use as much conversion averaging as allowed by sample requirements

- Long sample time is better, allows more time for VIN to settle

- Differential inputs buys performance because you’ll be subtracting system noise

- Avoid conversions with high speed communications i.e. DDR, USB, serial

- Perform ADC conversions in low-power modes for most “quiet” environment

Hardware

Grounds and power supplies

- We strongly recommend separate regulators for digital VDD and analog VDDA supplies, though they need to set to the same level.

- No inductive coupling between VSS and VSSA

- Use isolated digital and analog planes resistively coupled (0W) at a “starpoint” directly underneath VSSA pin/ball.

- There should be two ground planes, one for digital and a second for analog.

- The board designer needs to avoid overlap of the digital ground plane with the analog ground plane

- Analog signals and analog power should remain closely coupled with the analog ground plane.

- Separate regulators for digital and analog supplies

- Even better to provide an independent regulator for VREFH

- Large “tank” caps at the regulator output for stability, decoupling caps of various values very close to the DUT. 10uF capacitors should be placed on power inputs (VDD, VDDAD, VREFH)

Inputs

- Keep source resistance as low as possible.

- The differential inputs need to layed out in matched pairs in a side-to-side design. Ground and power planes over the analog inputs should minimize through-hole vias to provide the best possible shield over the input signals.

- Differential pair traces should be as close together as allowed for. Use VDDA and AGND to build a sort of coax shield around the signal pairs and try to separate digital signals/power/ground from analog signals/power/ground.

- For 16-bit performance, customers should strongly consider buffering the inputs

- An input buffer and low pass filter may be necessary for some ADC modules. If the ADC input has a “kick-back” when sampling then an input buffer can reduce source impedance and source signal disruption. Caution should be used when choosing an amplifier for buffer circuit to make sure the amplifier’s specifications matches or exceeds the ADC specifications. Even a unity gain amplifier will have some gain and offset. A means for trimming the buffer should be added to circuit.

Trace routing

- Keep digital traces away from analog supply, ADC reference, and ADC inputs. This means vertically as well as horizontally (and will likely mean more layers for customer boards).

- Keep analog power and traces as short as possible

To summarize the ADC performance won’t be the optimal by just loading different software. It’s very depended to the application requirements and the amount of best practices that can be adopt.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I did a quick test with one of our custom boards. Since I have not used your files, these are my settings:

16 bit differential input, (source is buffered with an OP because of the low input resistance of the ADC)

Acquisition time is about 230us (with maximum hardware averaging and long delays)

Reference voltage is 3.3V

For my purposes I record 4 different channels every second.

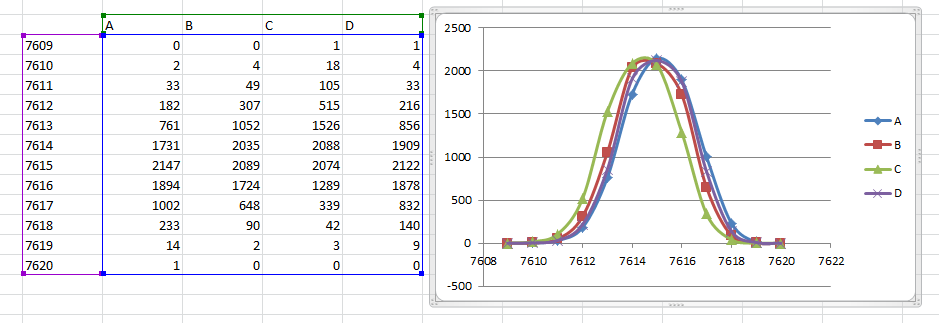

The following histogram is from 1 channel measured 4 times with 8000 data points each.

So I get better results. even slightly better than your scanB. I also checked that the width of the distribution stays almost the same across the full input voltage range.(increasing a little for higher voltages)

It would be interesting to see how to get the best results, so the more data to compare the more we will know.