- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- K70 reset pin state

K70 reset pin state

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

K70 reset pin state

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

On the K70 when a watchdog reset occurs the state of the RESET_b pin does not change.

Is this correct?

The manual implies that it should go low when a watchdog reset occurs.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Stephen Chorlton:

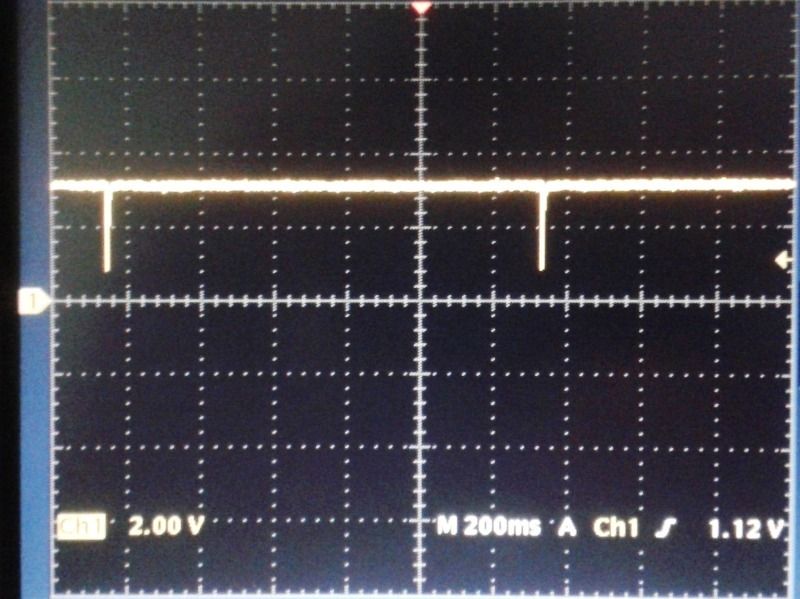

The Reset_b pin is expected to assert (change from high to low) with a watchdog reset. I took the next scope image from a TWR-K70F120M constantly resetting by the watchdog:

Are you using a custom board? Can you show the schematics for the Reset_b pin connection?

Regards!,

Jorge Gonzalez

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Jorge,

Thanks for the prompt reply.

I have some more information regarding our problem.

We do see a pulse on the Reset_b pin when I deliberately cause a reset via the watchdog.

The problem we have is if the clock source to the K70 fails. Clock is sourced from an external phy chip.

This causes the watchdog to go off (watchdog clocked by LPO), but we do not see a pulse on the Reset_b line.

Is the reset pulse driven by the input clock?

The underlying problem is that we require the reset pulse to reset the phy chip and restart the clock.

Regards,

Steve

Stephen Chorlton | Software Engineer

Tel: +44 1323 525313 | Steve.Chorlton@edwardsvacuum.com<mailto:Steve.Chorlton@edwardsvacuum.com>

15 Marshall Road, Eastbourne, East Sussex, BN22 9BA, UK | www.edwardsvacuum.com<http://www.edwardsvacuum.com/>;

Edwards Ltd | Registered in England and Wales No. 6124750

Registered office: Manor Royal, Crawley, West Sussex RH10 9LW