- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- K60 Flexbus Performance

K60 Flexbus Performance

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

K60 Flexbus Performance

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Since the internal RAM capacity is not sufficient, we plan to use external SRAM interfaced on flexbus.

What is the impact in performance when using external SRAM connected to flexbus instead of internal RAM ?

What is the Maximum Size of SRAM that can be connected to FlexBus?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am thinking to use the flexbus to connect a CPLD (16bits of register) with the microcontroller K60. I would like to know if it would be possible to use 16-bit data bus mode and address in multiplexed operating modes. It means, using the FB_AD[16:31] for data and address.

BR.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Juan,

It should be no problem for your case at all.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am reading the datasheet and I have found this:

• Address lines : FB_AD from FB_AD0 upward

• Data lines

• If CSCR[BLS] = 0, FB_AD from FB_AD31 downward

• If CSCR[BLS] = 1, FB_AD from FB_AD0 upward

In my application I have a device with 16 bits of data and 16 bits of address. I want to use the FB_AD in this way:

Address:FB_AD[16:31]

Data: FB_AD[16:31]

Would it be possible to set up in this way and how I should configure the registers FB_CSPMCR ,FB_CSCRn and FB_CSMRn ?

BR.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Juan,

I think you have to use FB_AD[1:16] to connect with the address lines of the device, data connection should be fine, and for flexbus initialization, please kindly refer to the following sample code for details.

void TWRK60_flexbus_init(void){

/* Enable the FlexBus */

/* Configure the FlexBus Registers for 8-bit port size */

/* with separate address and data using chip select 0 */

/* These configurations are specific to communicating with */

/* the MRAM used in this example */

/* For K60 tower module - do not set byte lane shift so that data */

/* comes out on AD[31:24] */

//Set Base address

FB_CSAR0 = (uint32)&MRAM_START_ADDRESS;

FB_CSCR0 = FB_CSCR_PS(1) // 8-bit port

| FB_CSCR_AA_MASK // auto-acknowledge

| FB_CSCR_ASET(0x1) // assert chip select on second clock edge after address is asserted

| FB_CSCR_WS(0x1) // 1 wait state - may need a wait state depending on the bus speed

;

FB_CSMR0 = FB_CSMR_BAM(0x7) //Set base address mask for 512K address space

| FB_CSMR_V_MASK //Enable cs signal

;

//enable BE signals - note, not used in this example

FB_CSPMCR = 0x02200000;

//fb clock divider 3

SIM_CLKDIV1 |= SIM_CLKDIV1_OUTDIV3(0x3);

/* Configure the pins needed to FlexBus Function (Alt 5) */

/* this example uses low drive strength settings */

//address

PORTB_PCR11 = PORT_PCR_MUX(5); // fb_ad[18]

PORTB_PCR16 = PORT_PCR_MUX(5); // fb_ad[17]

PORTB_PCR17 = PORT_PCR_MUX(5); // fb_ad[16]

PORTB_PCR18 = PORT_PCR_MUX(5); // fb_ad[15]

PORTC_PCR0 = PORT_PCR_MUX(5); // fb_ad[14]

PORTC_PCR1 = PORT_PCR_MUX(5); // fb_ad[13]

PORTC_PCR2 = PORT_PCR_MUX(5); // fb_ad[12]

PORTC_PCR4 = PORT_PCR_MUX(5); // fb_ad[11]

PORTC_PCR5 = PORT_PCR_MUX(5); // fb_ad[10]

PORTC_PCR6 = PORT_PCR_MUX(5); // fb_ad[9]

PORTC_PCR7 = PORT_PCR_MUX(5); // fb_ad[8]

PORTC_PCR8 = PORT_PCR_MUX(5); // fb_ad[7]

PORTC_PCR9 = PORT_PCR_MUX(5); // fb_ad[6]

PORTC_PCR10 = PORT_PCR_MUX(5); // fb_ad[5]

PORTD_PCR2 = PORT_PCR_MUX(5); // fb_ad[4]

PORTD_PCR3 = PORT_PCR_MUX(5); // fb_ad[3]

PORTD_PCR4 = PORT_PCR_MUX(5); // fb_ad[2]

PORTD_PCR5 = PORT_PCR_MUX(5); // fb_ad[1]

PORTD_PCR6 = PORT_PCR_MUX(5); // fb_ad[0]

//data

PORTB_PCR20 = PORT_PCR_MUX(5); // fb_ad[31] used as d[7]

PORTB_PCR21 = PORT_PCR_MUX(5); // fb_ad[30] used as d[6]

PORTB_PCR22 = PORT_PCR_MUX(5); // fb_ad[29] used as d[5]

PORTB_PCR23 = PORT_PCR_MUX(5); // fb_ad[28] used as d[4]

PORTC_PCR12 = PORT_PCR_MUX(5); // fb_ad[27] used as d[3]

PORTC_PCR13 = PORT_PCR_MUX(5); // fb_ad[26] used as d[2]

PORTC_PCR14 = PORT_PCR_MUX(5); // fb_ad[25] used as d[1]

PORTC_PCR15 = PORT_PCR_MUX(5); // fb_ad[24] used as d[0]

//control signals

PORTB_PCR19 = PORT_PCR_MUX(5); // fb_oe_b

PORTC_PCR11 = PORT_PCR_MUX(5); // fb_rw_b

PORTD_PCR1 = PORT_PCR_MUX(5); // fb_cs0_b

PORTD_PCR0 = PORT_PCR_MUX(5); // fb_ale

}

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Kan_Li,

I know that the flexbus is able to work in the way you mention. However, my question is if it is possible to employ the upper bus for the address( FB_AD[16:31]). For instance, the data bus can be placed either in the lower or upper of the bus. With the address bus is possible to work in the same way.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Juan,

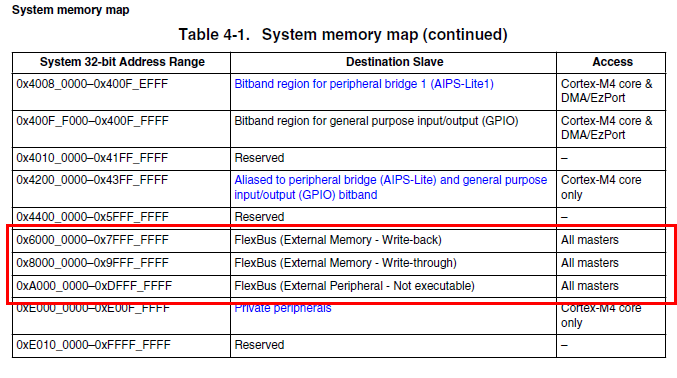

Actually I dont think it is possible to put address info on FB_AD[16:31] as this would exceed the address range mapping for flexbus , for example, if you want to access the data in 0xFFFF, you have to set the address pointer pointing to 0xFFFF0000 to drive 0xFFFF on FB_AD[16:31], but from RM, 0xA000_0000–0xDFFF_FFFF is the max mapping address range for flexbus. so that data info would not be driven on FB_AD[16:31] either.

Hope that helps,

Have a great day,

Kan

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

FlexBus timing is based on the FB_CLK signal, and it is 50MHz at max, while SRAM is based on the system clock, which is 100MHz or 120MHz depending on the part number, but if you select 120/150MHz part, which can enable cache for flexbus, so that would help to increase the performance. and there are 32 address lines available for this interface, but to enable the cache feature, the maximum size of SRAM can be 512MB. please kindly refer to the following for details.

Hope that helps,

B.R

Kan

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

SRAM is asynchronous. Then what is the significance of FB_CLK?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello Sithara,

have this worked for you? Please keep us posted, we'd like to know.

Best regards,

Monica

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have now planned to use DDR SDRAM interface and hence moved on to K61 processor with DDR interface.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

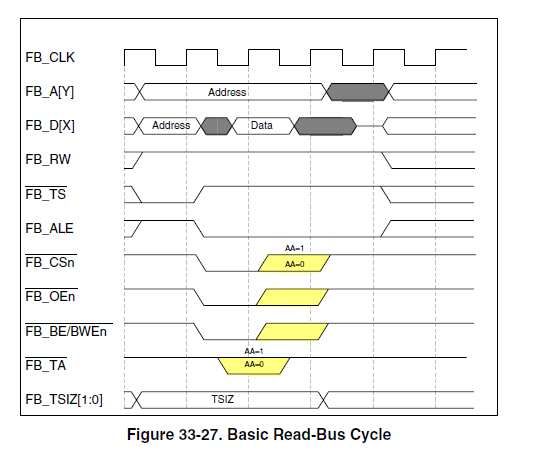

Yes, I know external SRAM might be asynchronous, but the timing for signals of flexBus is based on FB_CLK, for example, the following figure shows the basic reading process of the flexBus.

so FB_CLK's frequency impacts the flexBus performance.

Please kindly let me know if you have any issue.

B.R

Kan