- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: FTM Input capture mode ( single edge / dual edge capture mode) maximum input frequency

FTM Input capture mode ( single edge / dual edge capture mode) maximum input frequency

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FTM Input capture mode ( single edge / dual edge capture mode) maximum input frequency

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP stuff,

Now I am working on NXP FRDM-K64F, I am trying to implement a frequency measurement module.

I am using SDK example and make some modification.

I have tried single edge and dual edge capture mode. and finally I found there dual edge has better performance than single edge capture mode.

Then, I was try to test the cap frequency, because base on the document ( Document Number: K64P144M120SF5RM, Rev. 2, January 2014) , it mentioned " Note that the maximum frequency for the channel input signal to be detected correctly is system clock divided by 4, which is required to meet Nyquist criteria for signal sampling." ( chapter 40.4.4, page 1011) . I believe dual edge capture mode should has same requirement ( please correct me if I am wrong )

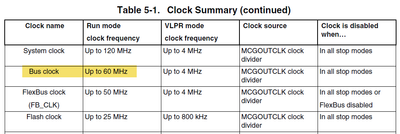

According to the example code, FTM using System clock ( which is bus clock), default bus clock is half of core clock ( 60MHz), and I have change it to 120MHz in my test code.

I have test the input frequency from 10KHz to 30MHz, but I found some issue :

- I can only measure up to 15MHz, and the result will become incorrect once frequency higher than it, I believe it because of ISR processing time is quite long, therefore I believe use DMA can help me solve this issue, am I right?

- when the frequency between 11MHz to 12MHz there has no interrupt been received(cannot enter ISR handler), I am not sure it's design feature or my hardware issue.

- when the frequency higher than 20MHz, there has no interrupt been received (cannot enter ISR handler), I believe it because the captured frequency has caped, therefore FTM hardware module cannot generate interrupt to NVIC. but according to the document, the maximum frequency should be 30MHz ( bus clock / 4) , that makes me very confuse. did I misunderstand ?

my source code has been attached, and the original example project is : frdmk64f_ftm_dual_edge_capture

please kindly assist, thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

First thing here that caught my attention here is that you are exceeding the bus clock maximum frequency. Please check the table below from the reference manual.

Please try to use bus clock withing the allowed range. I think this could be the main issue of the incorrect frequency you are measuring.

Best regards,

Felipe

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored. Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

Currently I am using eDMA to grab data from CnV for single edge capture mode and dual edge capture mode.

Bus clock is 60MHz

Based on the document, theoretically the maximum frequency can be captured is clock/4 = 15MHz,

And as I mentioned, there has no interrupt generated once frequency exceed 10MHz which is clock/6

Now, I found a weird behavior, the CnV value will become incorrect when the input signal frequency between 7MHz to 10MHz ( such as : input frequency is 8MHz, but the calculated result is 4MHz which base on the captured count)

last time I thought it is because of ISR speed too slow, so I think eDMA should can solve this issue. but base on the weird behaviors, it looks like hardware issue. ( because the result for using DMA is same as I use FTM interrupt )

So, is this behaviors caused by the hardware limitation ? or do you have any example can capture input signal frequency up to 15MHz ?

Thanks & Best Regards

Joshua

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joshua,

Unfortunately, we do not have more example to share than what is already included in the SDK. I agree that ISR could indeed add delay due to interrupt latency. I am also thinking this could be related to SW overhead that could be caused by SDK and drivers.

Also from what I could see in the different thread you are submitting here: https://community.nxp.com/t5/Kinetis-Microcontrollers/Input-Edge-Capture-Mode-Upper-Limiting-Frequen... you are using printf so this could be interfering as well.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

Thank you for your reply.

The PRINTF is not in ISR thread, does it still affect the speed ?

in order to avoid ISR processing speed issue , I have change the ISR implementation to eDMA . and I have disable FTM filter. but the behaviors is till unexpected:

eDMA captured value is unexpected when the input signal frequency exceed 7MHz ( as I said before, calculated result is 4MHz for a 8MHz input signal)

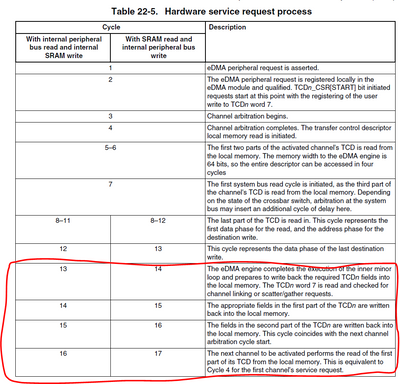

at first I thought it's eDMA performance issue, but according to description of eDMA : chapter 22.4.4.3

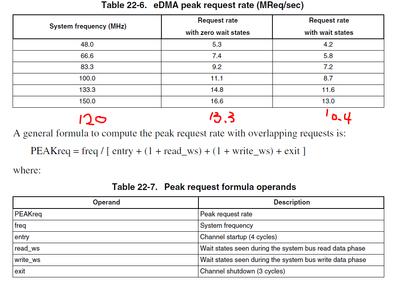

“For an internal peripheral bus to SRAM transfer, PEAKreq = 150 MHz / [ 4 + (1 + 2) + (1 + 1) + 3 ] cycles = 12.5 Mreq/sec”

The example system operates at 150MHz, and our system operates at 120MHz, so the PEAKreq should be 10Mreq/sec

therefore my understanding is : eDMA should not affect the result when the input signal frequency below 10MHz, did my understanding correct?

If I am right, then it become FTM hardware performance issue again. could you help me to double confirm with your hardware design team?

Thanks & Best Regards

Joshua

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joshua,

Thank you for your reply. Just want to let you know that I am currently checking this with our internal team to see if there is an issue with FTM module. I will let you know as soon as I receive an update.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joshua,

I have received confirmation from internal team, it seems that is expected behavior, please check below.

That is a normal behavior and the reasoning as follows:

As you said: *maximum frequency can be captured is clock/4 = 15MHz.*. so the min. time quanta is 1/15Mhz = 0.066666666us. for example, your input signal is 8Mhz, 50% duty cycle PWM. the time between two falling edge is 1/8Mhz = 0.125us

so if you measure 8Mhz, the CnV value will be 0.125 / 0.0666 = 1.87. this can either possible results a 1 or 2 in CnV resistor. which you only get 15Mhz or 7.5Mhz. (I don't why customer got a 4Mhz result..)

In a word, the FTM's input clock must be high enough compared with input signal, to get a correct measurement result.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

Thank you for your reply.

1st, I am agree with your colleague, so what I did in the experiment is :

- I use DMA to grab the CnV value to ram (array) - it can grab 100 times according to the array size

- calculate the difference between each two array element : array[1] - array[0] ...

- calculate the frequency based on the difference

- calculate the average value to get the final frequency

2nd, for the 4MHz result I had a suspicion:

- Input signal is 8MHz, and interrupt (First Interrupt) has been generated once rising edge been captured

- Then eDMA been kick start when FTM capture mode interrupt been received (First Interrupt)

- eDMA copy CnV value to ram

- And then Second interrupt been generated before eDMA finish current round, therefore Second interrupt been ignored ( interrupt happend between cycle 13-16 / 14-17)

- And then Third interrupt been generated to kick eDMA start second round ....

Therefore the calculated result been halved.

But, it is inconsistent with the description in the user manual if my suspicion is correct. eDMA performance should able to process 10M request when system frequency is 120MHz

and FTM input capture mode could generated interrupt correctly when input frequency below 15MHz.

So I don't know which module has slow down the system... that makes me confused. could you give me some help.

Thanks & Best Regards

Joshua

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Joshua,

Your experiment is not totally clear to me but as mentioned I think this is limitation of the FTM module so I do not think you can achieve such high frequency with input capture mode. Sorry for the inconvenience.

Best regards,

Felipe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Felipe,

Thank you for your reply and your suggestion.

Actually I have tested 60MHz also, the interrupt cannot be received once the input frequency exceed 10MHz, that is similar like 120MHz : interrupt cannot be received once the input frequency exceed clock_freq/6 which is different as the document mentioned clock_freq/4.

That makes me quite confused, do you have any idea ?

Thanks & Best Regards

Joshua