- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Does the KL26 have a fractional clock divider for use with I2S?

Does the KL26 have a fractional clock divider for use with I2S?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Does the KL26 have a fractional clock divider for use with I2S?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

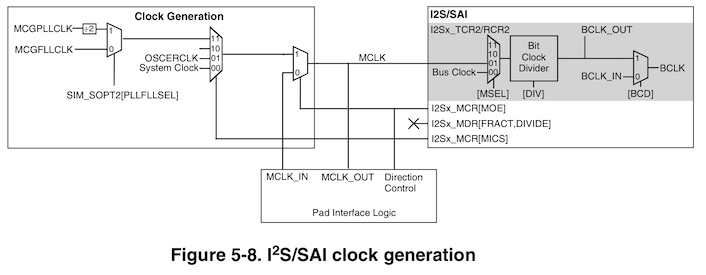

There are two diagrams in the reference manual, one on pg.137 (in the general clock generation section) which does not have a fractional clock divider:

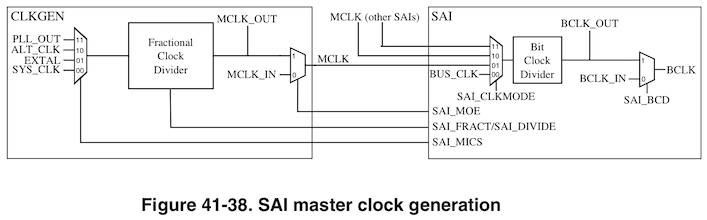

and the diagram on pg.831 (in the I2S section) which does have one:

On page 832 there is also a description of how it is used:

"The MCLK fractional clock divider uses both clock edges from the input clock to

generate a divided down clock that will approximate the output frequency, but without

creating any new clock edges. Configuring FRACT and DIVIDE to the same value will

result in a divide by 1 clock, while configuring FRACT higher than DIVIDE is not

supported. The duty cycle can range from 66/33 when FRACT is set to one less than

DIVIDE down to 50/50 for integer divide ratios, and will approach 50/50 for large noninteger

divide ratios. There is no cycle to cycle jitter or duty cycle variance when the

divide ratio is an integer or half integer, otherwise the divider output will oscillate

between the two divided frequencies that are the closest integer or half integer divisors of

the divider input clock frequency. The maximum jitter is therefore equal to half the

divider input clock period, since both edges of the input clock are used in generating the

divided clock."

After some experimentation, it seems like the FRACT/DIVIDE register doesn't do anything - so guessing that the first diagram (without a MCLK divider) is what is actually there. Can someone confirm this? Or is there a way to enable the FRACT/DIVIDE functionality? This would be really useful to have - as otherwise I need to use an off chip PLL or another crystal to generate an audio clock of the right frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Fred,

Yes , you are right , I2S module on kl26 does not support fractional divider, we can find on here :

"The module's MCLK Divide Register (MDR) is not used to control MCLK generation." on the page 109 of RM.

So there on one side, you can config the I2S clock as you said use a dedicated oscillator for your need,

or reconfiguration the PLL.

Best Regards,

Alice

------------------------------------------------------------------------------------------

If this post answers your question, please click the Correct Answer button.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Alice,

Can you tell me please, does the KL16 have this fractional divider, or not?

Regards,

Alexander

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

KL16RM 3.9.4.3.4 has the same statement: "The module's MCLK Divide Register (MDR) is not used to control MCLK generation." It can be a 'challenge' reading the Kinetis Reference-Manuals, because the 'peripheral sections' are copied-in 'boiler plate' generic references for the silicon-macros, and 'Chapter 3' of each manual lists all the little 'by the way' details that say how they got hooked-up at the chip level, and the details can range from the definition of 'system clock' for SPI (Bus clock, of course, not ACTUAL system clock, despite the fact that the example tables are all showing 100MHz), and this MCLK block that is 'bypassed entirely' in the KL series.

In any case, you will find that an audio MCLK with 'the maximum one half input clock jitter' on it will be VERY unsatisfactory.

You might look at Maxim AN5477, especially Figure 8.