- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- General Purpose Microcontrollers

- :

- Kinetis Microcontrollers

- :

- Re: 5v Tolerant pins as Open Collector Drivers

5v Tolerant pins as Open Collector Drivers

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

As I was reviewing the datasheets/reference manuals of the MK21FX512VMD12 and MK22FN1M0AVMD12, I noticed that there was the comment that all GPIO pins are 5V tolerant.

Going through the questions about this previously, it seems that only the input functionality of the pins are 5V tolerant, the outputs (even if they are in open drain mode) engage the anti-static diodes to the chip's Vdd and are only tolerant to what Vdd which is a maximum of 3.6V.

In my application, I have a number of pins that are driving NPN transistors as open collectors drivers to 5V circuitry and I was wondering:

Could I use the pins as 5V open drain outputs if, when the driver is disabled the pin is in input mode (and is 5V tolerant) and when I want to pull the line low (which the NPN transistor was doing) change to output mode with a low output?

It's certainly no less kludgy than using the NPN transistor, and it saves me $0.05 in each instance.

Thanx!

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If get rid of the transistors watch the total package sink current that is allowable on Vss.

Getting close to that can cause ground bounce problems during load switching, if many outputs transition at the same time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If get rid of the transistors watch the total package sink current that is allowable on Vss.

Getting close to that can cause ground bounce problems during load switching, if many outputs transition at the same time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

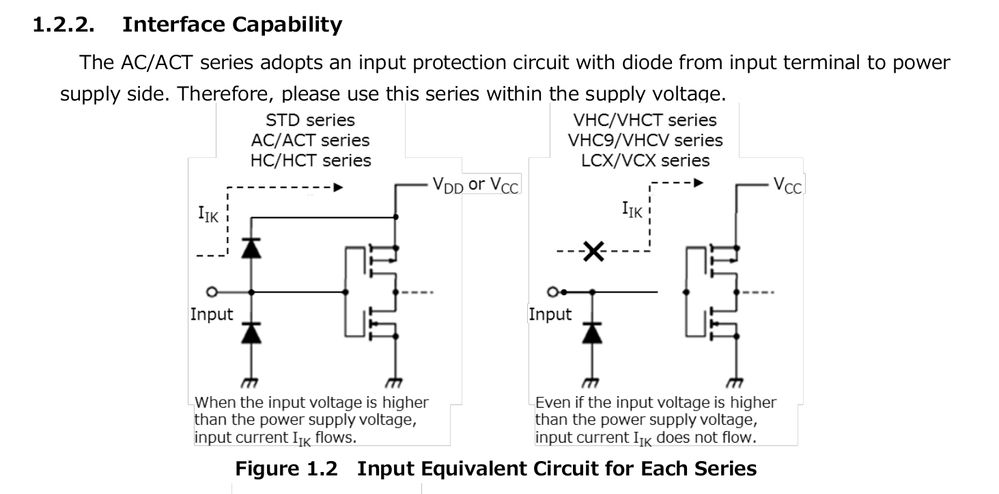

In one case the pins are driving the inputs to a TC74AC138FTEL (CMOS Logic) with an equivalant input of:

So I think I can use a 100k for the pull up.

In the other case, it's five PNP transistors (MMBTA06LT1G - Hfe of 100) of which only one should be active at any time that will need a maximum of 200mA through it, which means I should be drawing 2mA through it.

When I do a power inventory, according to the Datasheet, Idd_run (Run mode current - all peripheral clocs enabled, code executing from flash) = 49.9mA (I obviously use 50mA for my calculations). The current application circuit's peripheral total worst case (which shouldn't happen) current sink from all peripherals active = 103mA. The maximum current draw for normal operation is 84mA. Remove the NPN transistors will drop the worst possible case number to 86mA and the normal operation maximum current sink to 66mA. It also provides me with a cost reduction of about $0.45 per PCB.

Idd (Total sink current for the device) = 185mA so in any case I'm not exceeding the total sink for the device so I think I'm good.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes current sounds reasonable.

185mA in a small package does fell a bit toasty.

Alas those static protection diodes are there for a reason. It is not clear to me if you are saying you are using the series without the protection diode to Vcc?

It becomes more of a board handling issue, physically, than run time issue.

Presumably all the normal anti-static precautions are taken to make that a non-issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

185mA at 3.3V is 0.61W in this package shouldn't get that "toasty", you're talking 169 mm^2 in area with a large Gnd and 3V3 Plans for heat dissipation - I haven't noticed any real increase in heat around the MCU (and I have been checking it with a thermal imaging camera).

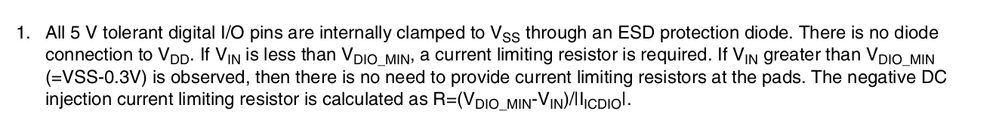

I'm not sure what you mean by "you are using the series without the protection diode to Vcc" - as I understand it (and it seems to be confirmed in multiple posts to this forum) that in the Kinetis, digital pins (not analog) in input mode do not have an ESD diode to Vdd. The datasheets have the note:

Again, it appears this is the case when the pin is in input mode but not any of the output modes (in those cases there is diode protection to Vdd).

So, the plan is to keep the IO pin in input mode until I need to sink current, at which point I will change the pin to an output (driving a low value). With a current limiting resistor, this should properly simulate an open collector output

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was referring to the Figure 1.2 for the VHC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry? I don't know what "VHC" is and none of the NXP documents have a Figure 1.2.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am refereeing to the TC74AC138FTEL image posted above, not the NXP part.

VHC without static diode to Vcc is on right.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey @bobpaddock

I modified a prototype PCB by taking out the NPN transistors as detailed here and things worked as expected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I should have looked there - I had moved on from the demuxer.

I'm using the TC74AC138FTEL (the left side of Figure 1.2), not the VHC. The AC has the ESD diodes in the input so there shouldn't be any worries.