- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpresso Software and Tools

- :

- Kinetis Design Studio

- :

- Re: Kinetis L: Clock Gating - Using Partial STOP1

Kinetis L: Clock Gating - Using Partial STOP1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Interested in reducing as much power a possible to my system while ADC is able to take a measurement. This requires Partial STOP1, with clock gating control...only enabling ADC clock, and disabling clocks from all peripherals and sleeping processor.

I found this post explaining STOP1, which I just learned of, and I can see in PE how this is enabled, etc:

Operation modes in Processor Expert

But how is the gate controlling done? I do not see additional option menus pop up once enables in PE? Am I going to have to dig through registers on my own or is there some options/directions guidance that can be given? Also, does PE generate the needed code to implement clock gating on specific peripherals?

Thanks,

-Peter

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

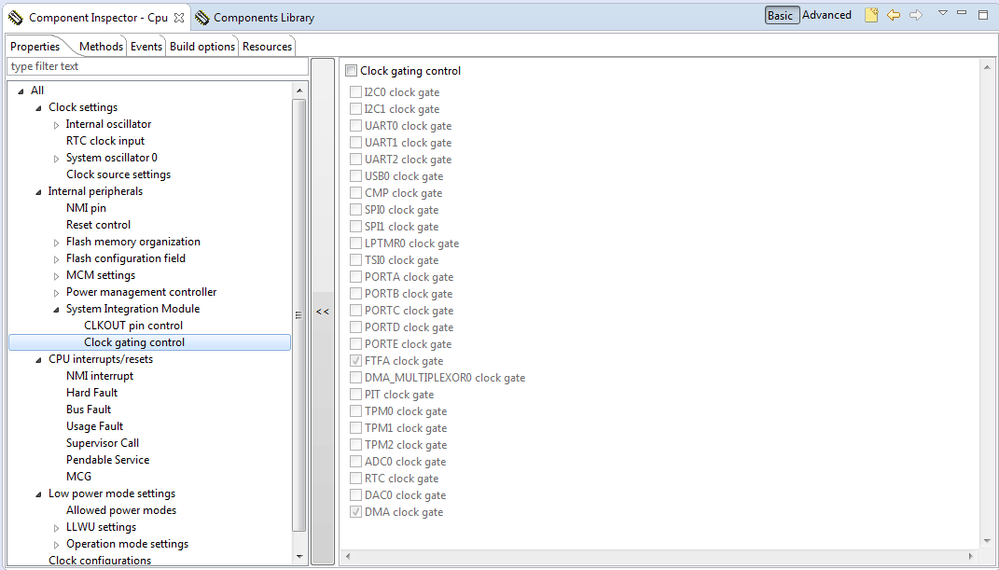

for KL25Z with LDD components, you can find clock gating in a processor component, Internal peripherals > System Integration Modules > Clock gating control:

The code is then placed into PE_low_level_init() function called during application startup.

In case of Processor Expert with Kinetis SDK there is System Integration Module initialization component, Init_SIM, where similar properties are available and code placed in the Init() function of this component.

Regards,

Lukas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Peter,

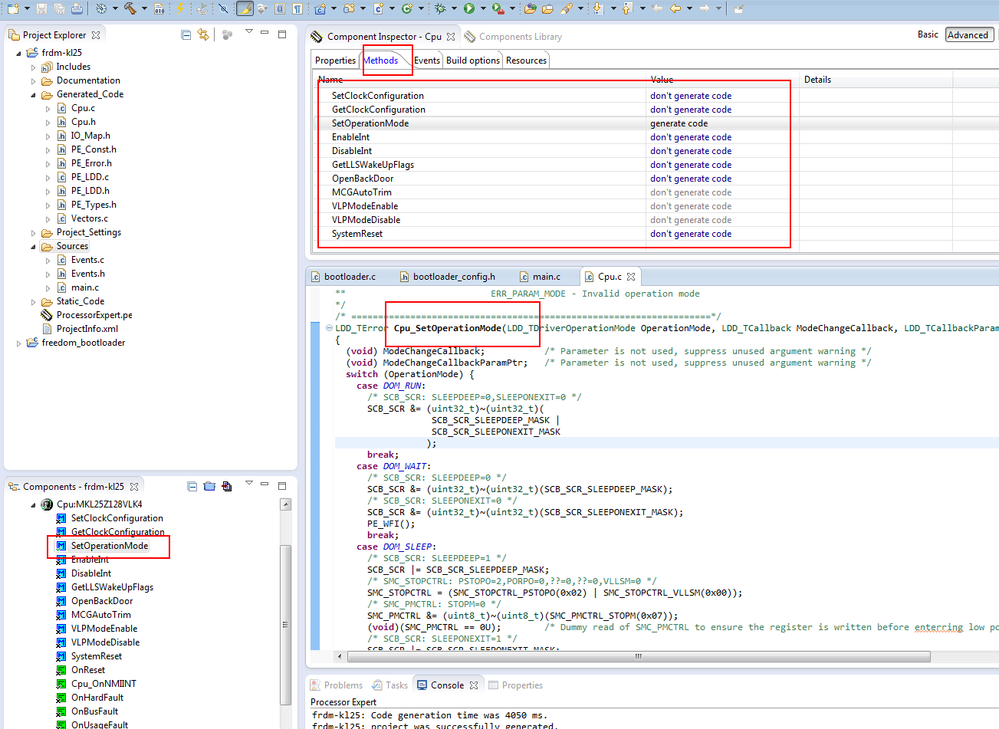

Yes, you can use the PE to configure the low power mode , after configure , the code will generate on the cpu.c file ,

and the register have be configured .

About the Low power , you can refer to

http://cache.freescale.com/files/microcontrollers/doc/app_note/AN4470.pdf?fsrch=1&sr=1&pageNum=1

and

http://cache.freescale.com/files/32bit/doc/app_note/AN4503.pdf?fsrch=1&sr=1&pageNum=1

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alice,

This is not what I asked. I know how to do this. In Partial Stop1, the post reference states I can clock gate perihperals to save power. I want to know the following:

1) I need to control clock gating of peripherals in Partial Stop 1, does PE generate this code? I do not see options in PE to generate this code. I wish to only have ADC clock running (ADC reading), while all other peripherals are shut down.

2) If PE does not generate this code? Are there examples of clock gating? What kinds of register sets are involved?

Thanks,

-Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Peter,

Yes, the PE generate the code :

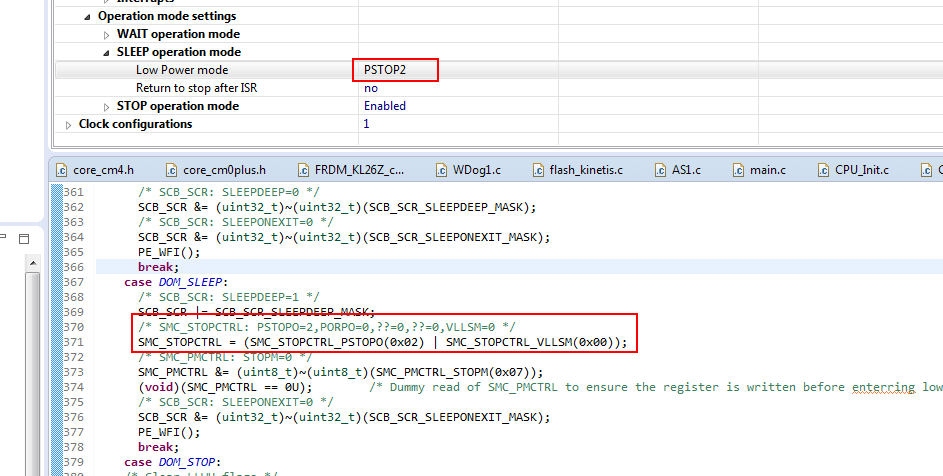

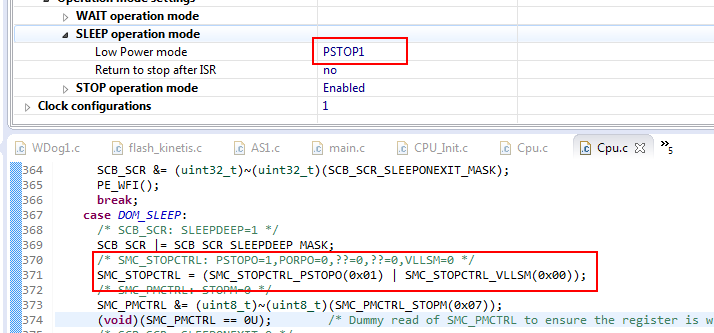

when you select the "STOP2" mode, you can see the generated code :

when you select "STOP1" mode , you can see :

And in stop1 mode , from the Reference manual : PSTOP1 - Partial Stop with both system and bus clocks disabled

so , i thin it can not use ADC .

Hope it helps

Alice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alice,

Thanks for replying again but this is not what I am asking, please read carefully.

I want to use Partial Stop Mode to turn off some of the peripherals, not the bus clock. I want to stop the clock on peripherals and disable them, this is known as clock gating. You're showing me the bus clock is stopped, I do not want to stop it, I want to stop it reaching peripherals, but not all.

Based on this post:

Operation modes in Processor Expert

You can clock gate peripherals. I wish to do THIS.

Example:

- CPU sleeps

- All Peripherals disabled and not receiving clock

- EXCEPT: ADC is running and taking a measurement, when this measurement is finished, I wish to wake up, read the value, and then re-enable all peripherals.

**There is no code from PE to control the clock gating for individual peripherals. IS there? if so where is it? if not, where can I find support on this?

Is there additional people who can help answer this question?

Thanks,

-Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Peter,

I suppose that you want to configure clock gate during execution of your application (before entering the partial stop mode).

The run-time settings of peripherals clock gates can be configured by using SIM PDD macros (see SIM_PDD.h source code file, SIM_PDD_SetClockGate() macro) when you are using Processor Expert project without Kinetis SDK.

If you are using Kinetis SDK you can use fsl_sim_hal component and SIM_HAL_EnableClock() and SIM_HAL_Disable() function of this HAL component.

Please note that you must prevent access to a device's registers when you disable the clock gate of the device. Otherwise the hard fault exception will be invoked.

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Lucas & Marek,

Thanks for your reply. I found these options under the CPU component properties, using your picture, but I am using the typical view

For others who may use this:

- Go to your CPU component Inspector

- Go to Internal Peripherals Tab

- Go to System Integration Module Sub-Tab

- Go to Clock gating sub-sub tab (haha)

- Enable clock Gating and which peripheral.

Thank you Marek & Lucas!

-Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Peter,

for KL25Z with LDD components, you can find clock gating in a processor component, Internal peripherals > System Integration Modules > Clock gating control:

The code is then placed into PE_low_level_init() function called during application startup.

In case of Processor Expert with Kinetis SDK there is System Integration Module initialization component, Init_SIM, where similar properties are available and code placed in the Init() function of this component.

Regards,

Lukas