- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Processors

- :

- i.MX Processors Knowledge Base

- :

- ISL79987 and adv7180 de-interlace driver for iMX8QXP boards

ISL79987 and adv7180 de-interlace driver for iMX8QXP boards

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Printer Friendly Page

- Report Inappropriate Content

ISL79987 and adv7180 de-interlace driver for iMX8QXP boards

ISL79987 and adv7180 de-interlace driver for iMX8QXP boards

adv7180 is the 8 bits parallel CSI interface TVin to iMX8QXP validation board.

Its weaving mode de-interlace can be supported on both iMX8QXP B0 and C0 chips, but blending mode de-interlace can only work on iMX8QXP C0 chips.

ISL79987 is the 4 virtual channel TVin chip which can input 4 CVBS cameras to iMX8QXP with MIPI CSI2 inteface, it can only work with iMX8QXP C0 chips. The iMX8QXP B0 chips have MIPI CSI2 virtual channel errata.

To test the capture to file:

$ /unit_tests/V4L2/mx8_v4l2_cap_drm.out -cam 1 -num 300 -fmt YUYV -of

To test the preview on screen:

$ killall weston

$ /unit_tests/V4L2/mx8_v4l2_cap_drm.out -cam 1 -fmt RGBP -num 30000

Note:

1. For weaving mode de-interlace, when the ISI is doing de-interlace, it can't do CSC at the same time, so preview will get color issue, because the real output video is always YUYV format.

2. For blending mode de-interlace, it must use ISI0, so for ISL79987, only one camera can use blending mode, the other three cameras are still using weaving mode. The preview color is OK for such use case.

3. The patch is for L4.19.35 BSP.

2019-11-14 update:

Add the test application "mx8_v4l2_cap_drm.tar.gz" to support YUYV render to display.

Test command to render 4 weaving mode cameras:

./mx8_v4l2_cap_drm.out -cam 0xF -fmt YUYV -num 30000

2020-04-29 update:

Add "0006-isl7998x-fix-the-mipi_bps-overwrite-issue-from-set_f.patch", it fixed the issue that MIPI bps information in isl7998x_data->format.reserved[0] had been overwritten by isl7998x_set_fmt().

2021-06-11 update:

Added the patches based on L5.4.70_2.3.0 GA BSP.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hello.

Do i.mx8mq support TVin architecture? Now I use adv7282m, Mipi CSI output. I have implemented the driver, but the Hal layer cannot collect data.

The driver architecture is designed according to the driver of isl79987 provided by you!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

/*

* Copyright 2019 NXP

*/

/*

* The code contained herein is licensed under the GNU General Public

* License. You may obtain a copy of the GNU General Public License

* Version 2 or later at the following locations:

*

* http://www.opensource.org/licenses/gpl-license.html

* http://www.gnu.org/copyleft/gpl.html

*/

#include <linux/module.h>

#include <linux/init.h>

#include <linux/slab.h>

#include <linux/ctype.h>

#include <linux/types.h>

#include <linux/delay.h>

#include <linux/clk.h>

#include <linux/of_device.h>

#include <linux/i2c.h>

#include <linux/v4l2-mediabus.h>

#include <linux/of_gpio.h>

#include <linux/pinctrl/consumer.h>

#include <linux/regulator/consumer.h>

#include <media/v4l2-subdev.h>

#include <linux/interrupt.h>

#define ADV7282M_IDENT 0x11 /* IDENT */

#define MIPI_CSI2_SENS_VC0_PAD_SOURCE 0

#define MIPI_CSI2_SENS_VCX_PADS_NUM 1

#define MAX_FPS 30

#define MIN_FPS 25

#define DEFAULT_FPS 30

/* adv7282m interrupt state bit*/

#define ADV7282M_SD_LOCK 0x01

#define ADV7282M_SD_UNLOCK 0X02

/* List of input video formats supported. The video formats is corresponding

* with v4l2 id in video_fmt

*/

typedef enum {

NTSC = 0, /* Locked on (M) NTSC video signal. */

PAL, /* (B, G, H, I, N)PAL video signal. */

} video_fmt_idx;

/*! Video format structure. */

typedef struct {

int v4l2_id; /*!< Video for linux ID. */

char name[16]; /*!< Name (e.g., "NTSC", "PAL", etc.) */

u16 width; /*!< Active width. */

u16 height; /*!< Active height. */

int frame_rate; /*!< Frame rate. */

} video_fmt_t;

/*! Description of video formats supported.

*

* PAL: raw=720x625, active=720x576.

* NTSC: raw=720x525, active=720x480.

*/

static video_fmt_t video_fmts[] = {

{ /*! NTSC */

.v4l2_id = V4L2_STD_NTSC,

.name = "NTSC",

.width = 720, /* ACT_FRM_WIDTH plus 1 */

.height = 480, /* ACT_FRM_WIDTH plus 1 */

.frame_rate = 30,

},

{ /*! (B, G, H, I, N) PAL */

.v4l2_id = V4L2_STD_PAL,

.name = "PAL",

.width = 720,

.height = 576,

.frame_rate = 25,

},

};

struct sensor_data {

struct v4l2_subdev subdev;

struct media_pad pads[MIPI_CSI2_SENS_VCX_PADS_NUM];

struct i2c_client *i2c_client;

struct i2c_client *client_csi_tx;

struct i2c_client *client_csi_i2p;

struct v4l2_mbus_framefmt format;

struct v4l2_captureparm streamcap;

char running;

u32 mclk;

u8 mclk_source;

struct clk *sensor_clk;

int v_channel;

bool is_mipi;

unsigned int chip_id;

int num_lanes;

video_fmt_idx video_id;

int rst_gpio;

int pwn_gpio;

struct mutex adv7282_lock;

};

struct sensor_data adv7282m_data;

static inline struct sensor_data *subdev_to_sensor_data(struct v4l2_subdev *sd)

{

return container_of(sd, struct sensor_data, subdev);

}

/*! Read one register from a adv7282m i2c slave device.

*

* @param *reg register in the device we wish to access.

*

* @return 0 if success, an error code otherwise.

*/

static inline int adv7282m_read_reg(struct sensor_data *adv7282m_data, u8 reg)

{

int val;

val = i2c_smbus_read_byte_data(adv7282m_data->i2c_client, reg);

if (val < 0) {

dev_info(&adv7282m_data->i2c_client->dev,

"%s:read reg error: reg=%2x\n", __func__, reg);

return -1;

}

return val;

}

/*! Write one register of a adv7282m i2c slave device.

*

* @param *reg register in the device we wish to access.

*

* @return 0 if success, an error code otherwise.

*/

static int adv7282m_write_reg(struct sensor_data *adv7282m_data, u8 reg, u8 val)

{

s32 ret;

ret = i2c_smbus_write_byte_data(adv7282m_data->i2c_client, reg, val);

if (ret < 0) {

printk("%s:write reg error:reg=%2x,val=%2x\n", __func__,

reg, val);

return -1;

}

return 0;

}

static int adv7282m_csi_write(struct sensor_data *adv7282m_data, unsigned int reg, unsigned int value)

{

int ret;

ret = i2c_smbus_write_byte_data(adv7282m_data->client_csi_tx, reg, value);

if(ret <0){

printk("%s:client_csi_i2p reg error: reg=0x%02x\n", __func__, reg);

return -1;

}

return ret;

}

static inline int adv7282m_csi_read(struct sensor_data *adv7282m_data, u8 reg)

{

int val;

val = i2c_smbus_read_byte_data(adv7282m_data->client_csi_tx, reg);

if (val < 0) {

dev_dbg(&adv7282m_data->client_csi_tx->dev,

"%s:csi_read reg error: reg=0x%02x\n", __func__, reg);

return -1;

}

return val;

}

static int adv7282m_vpp_write(struct sensor_data *adv7282m_data, unsigned int reg, unsigned int value)

{

int val;

val =i2c_smbus_write_byte_data(adv7282m_data->client_csi_i2p, reg, value);

if(val <0){

printk("%s:client_csi_i2p reg error: reg=0x%02x\n", __func__, reg);

return -1;

}

return val;

}

static inline int adv7282m_vpp_read(struct sensor_data *adv7282m_data,u8 reg)

{

int val;

val = i2c_smbus_read_byte_data(adv7282m_data->client_csi_i2p, reg);

if (val < 0) {

dev_dbg(&adv7282m_data->client_csi_i2p->dev,

"%s:client_csi_i2p reg error: reg=0x%02x\n", __func__, reg);

return -1;

}

return val;

}

static void adv7282m_hw_reset(struct sensor_data *adv7282m_data)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

gpio_set_value(adv7282m_data->rst_gpio, 0);

gpio_set_value(adv7282m_data->pwn_gpio, 1);

msleep(10);

gpio_set_value(adv7282m_data->rst_gpio, 1);

msleep(10);

}

/*

static irqreturn_t adv7282_isr(int irq, void *dev_id)

{

struct sensor_data *adv7282m_data = dev_id;

unsigned int intr;

char *unlock[2] = { "CVBS_STATE=DISCONNECTED", NULL };

char *lock[2] = { "CVBS_STATE=CONNECTED", NULL };

mutex_lock(&adv7282m_data->adv7282_lock);

//enter interrupt sub map

adv7282m_write_reg(adv7282m_data, 0x0E, 0x20);

intr = adv7282m_read_reg(adv7282m_data 0x42);

//clear intr

adv7282m_write_reg(adv7282m_data, 0x43, intr);

adv7282m_write_reg(adv7282m_data, 0x0E, 0x00);

mutex_unlock(&adv7282m_data->adv7282_lock);

if(ADV7282M_SD_LOCK & intr){

//connected

kobject_uevent_env(&adv7282m_data->i2c_client->dev.kobj, KOBJ_CHANGE, lock);

//adv7282_status = 1;

printk("%s,connected!\n",__func__);

}else if(ADV7282M_SD_UNLOCK & intr){

//lost connection

kobject_uevent_env(&adv7282m_data->i2c_client->dev.kobj, KOBJ_CHANGE, unlock);

//adv7282_status = 0;

printk("%s,disconnected!\n",__func__);

}

//adv7282m_intr_config(adv7282m_data->i2c_client);

return IRQ_HANDLED;

}

*/

static int adv7282m_hardware_init(struct sensor_data *adv7282m_data)

{

int retval = 0;

u8 data = 0;

struct i2c_client *client = adv7282m_data->i2c_client;

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

//dev_info(&adv7282m_data->i2c_client->dev, "In %s()\n", __func__);

// Init the adv7282m

//##CVBS AUTODETECT##

//:AUTODETECT CVBS Single Ended In Ain 1, MIPI Out:

adv7282m_write_reg(adv7282m_data,0x0F,0x00); //Exit Power Down Mode

adv7282m_write_reg(adv7282m_data,0x00,0x00); //INSEL = CVBS in on Ain 1

adv7282m_write_reg(adv7282m_data,0x0E,0x80); //ADI Required Write

adv7282m_write_reg(adv7282m_data,0x9C,0x00); //ADI Required Write

adv7282m_write_reg(adv7282m_data,0x9C,0xFF); //ADI Required Write

adv7282m_write_reg(adv7282m_data,0x0E,0x00); //Enter User Sub Map

adv7282m_write_reg(adv7282m_data,0x03,0x4E); //ADI Required Write

adv7282m_write_reg(adv7282m_data,0x04,0x57); //Power-up INTRQ pin

adv7282m_write_reg(adv7282m_data,0x13,0x00); //Enable INTRQ output driver

adv7282m_write_reg(adv7282m_data,0x17,0x41); // select SH1

adv7282m_write_reg(adv7282m_data,0x1D,0xC0); //Tri-State LLC output driver

adv7282m_write_reg(adv7282m_data,0x52,0xCD); //ADI Required Write

adv7282m_write_reg(adv7282m_data,0x80,0x51); //ADI Required Write (also in adv7180.c under linux4 / ADI recommended writes for improved video quality)

adv7282m_write_reg(adv7282m_data,0x81,0x51); //ADI Required Write (also in adv7180.c under linux4 / ADI recommended writes for improved video quality)

adv7282m_write_reg(adv7282m_data,0x82,0x68); //ADI Required Write (also in adv7180.c under linux4 / ADI recommended writes for improved video quality)

adv7282m_write_reg(adv7282m_data,0x5D,0x1C); //Enable Diagnostic pin 1 - Level=1.125V

adv7282m_write_reg(adv7282m_data,0x5E,0x1C); //Enable Diagnostic pin 2 - Level=1.125V

adv7282m_write_reg(adv7282m_data,0xFD,0x84); //Set VPP Map Address

adv7282m_write_reg(adv7282m_data,0xFE,0x88); //Set CSI Map Address

msleep(10);

return retval;

}

static int adv7282m_g_std(struct v4l2_subdev *sd, v4l2_std_id *norm)

{

v4l2_std_id std;

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

u8 data;

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

// Page 1

/*adv7282m_write_reg(adv7282m_data, 0xFF, 0x01);

data = (u8)adv7282m_read_reg(adv7282m_data, 0x1C);

data &= 0x70;*/

/*if ((data == 0x10) || (data == 0x20) || (data == 0x50)) {

std = V4L2_STD_PAL;

adv7282m_data->video_id = PAL;

} else {*/

std = V4L2_STD_NTSC;

adv7282m_data->video_id = NTSC;

//}

if (norm != NULL)

*norm = std;

return 0;

}

static int adv7282m_g_parm(struct v4l2_subdev *sd, struct v4l2_streamparm *a)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

struct v4l2_captureparm *cparm = &a->parm.capture;

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

int ret = 0;

switch (a->type) {

/* This is the only case currently handled. */

case V4L2_BUF_TYPE_VIDEO_CAPTURE:

case V4L2_BUF_TYPE_VIDEO_CAPTURE_MPLANE:

memset(a, 0, sizeof(*a));

a->type = V4L2_BUF_TYPE_VIDEO_CAPTURE;

cparm->capability = adv7282m_data->streamcap.capability;

cparm->timeperframe = adv7282m_data->streamcap.timeperframe;

cparm->capturemode = adv7282m_data->streamcap.capturemode;

ret = 0;

break;

/* These are all the possible cases. */

case V4L2_BUF_TYPE_VIDEO_OUTPUT:

case V4L2_BUF_TYPE_VIDEO_OVERLAY:

case V4L2_BUF_TYPE_VBI_CAPTURE:

case V4L2_BUF_TYPE_VBI_OUTPUT:

case V4L2_BUF_TYPE_SLICED_VBI_CAPTURE:

case V4L2_BUF_TYPE_SLICED_VBI_OUTPUT:

ret = -EINVAL;

break;

default:

pr_debug(" type is unknown - %d\n", a->type);

ret = -EINVAL;

break;

}

return ret;

}

/*!

* ioctl_s_parm - V4L2 sensor interface handler for VIDIOC_S_PARM ioctl

* @s: pointer to standard V4L2 device structure

* @a: pointer to standard V4L2 VIDIOC_S_PARM ioctl structure

*

* Configures the sensor to use the input parameters, if possible. If

* not possible, reverts to the old parameters and returns the

* appropriate error code.

*/

static int adv7282m_s_parm(struct v4l2_subdev *sd, struct v4l2_streamparm *a)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

int ret = 0;

switch (a->type) {

/* This is the only case currently handled. */

case V4L2_BUF_TYPE_VIDEO_CAPTURE:

case V4L2_BUF_TYPE_VIDEO_CAPTURE_MPLANE:

break;

/* These are all the possible cases. */

case V4L2_BUF_TYPE_VIDEO_OUTPUT:

case V4L2_BUF_TYPE_VIDEO_OVERLAY:

case V4L2_BUF_TYPE_VBI_CAPTURE:

case V4L2_BUF_TYPE_VBI_OUTPUT:

case V4L2_BUF_TYPE_SLICED_VBI_CAPTURE:

case V4L2_BUF_TYPE_SLICED_VBI_OUTPUT:

pr_debug(" type is not "\

"V4L2_BUF_TYPE_VIDEO_CAPTURE but %d\n",

a->type);

ret = -EINVAL;

break;

default:

pr_debug(" type is unknown - %d\n", a->type);

ret = -EINVAL;

break;

}

return ret;

}

static int adv7282m_enum_mbus_code(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_mbus_code_enum *code)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

code->code = adv7282m_data->format.code;

return 0;

}

/*!

* adv7282m_enum_framesizes - V4L2 sensor interface handler for

* VIDIOC_ENUM_FRAMESIZES ioctl

* @s: pointer to standard V4L2 device structure

* @fsize: standard V4L2 VIDIOC_ENUM_FRAMESIZES ioctl structure

*

* Return 0 if successful, otherwise -EINVAL.

*/

static int adv7282m_enum_framesizes(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_frame_size_enum *fse)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

if (fse->index > PAL)

return -EINVAL;

fse->max_width = max(video_fmts[fse->index].width, video_fmts[fse->index].width);

fse->min_width = fse->max_width;

fse->max_height = max(video_fmts[fse->index].height, video_fmts[fse->index].height);

fse->min_height = fse->max_height;

return 0;

}

static int adv7282m_enum_frame_interval(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_frame_interval_enum *fie)

{

int i, count;

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

if (fie->index < 0 || fie->index > PAL)

return -EINVAL;

if (fie->width == 0 || fie->height == 0 ||

fie->code == 0) {

pr_warning("Please assign pixel format, width and height.\n");

return -EINVAL;

}

fie->interval.numerator = 1;

/* TODO Reserved to extension */

count = 0;

for (i = 0; i < PAL; i++) {

if (fie->width == video_fmts[i].width

&& fie->height == video_fmts[i].height) {

count++;

}

if (fie->index == (count - 1)) {

fie->interval.denominator = video_fmts[i].frame_rate;

return 0;

}

}

return -EINVAL;

}

static int adv7282m_get_fmt(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_format *fmt)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

struct v4l2_mbus_framefmt *mf = &fmt->format;

if (fmt->pad)

return -EINVAL;

mf->code = adv7282m_data->format.code;

mf->width = adv7282m_data->format.width;

mf->height = adv7282m_data->format.height;

mf->colorspace = adv7282m_data->format.colorspace;

mf->field = adv7282m_data->format.field;

mf->reserved[0] = adv7282m_data->format.reserved[0];

return 0;

}

static int adv7282m_set_fmt(struct v4l2_subdev *sd,

struct v4l2_subdev_pad_config *cfg,

struct v4l2_subdev_format *fmt)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

struct v4l2_mbus_framefmt *mf = &fmt->format;

if (fmt->pad)

return -EINVAL;

mf->code = adv7282m_data->format.code;

mf->colorspace = adv7282m_data->format.colorspace;

mf->field = V4L2_FIELD_INTERLACED;

if (fmt->which == V4L2_SUBDEV_FORMAT_TRY)

return 0;

memcpy(&adv7282m_data->format, &fmt->format, sizeof(struct v4l2_mbus_framefmt));

return 0;

}

static int adv7282m_get_frame_desc(struct v4l2_subdev *sd, unsigned int pad,

struct v4l2_mbus_frame_desc *fd)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

return 0;

}

static int adv7282m_set_frame_desc(struct v4l2_subdev *sd,

unsigned int pad,

struct v4l2_mbus_frame_desc *fd)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

return 0;

}

static int adv7282m_set_power(struct v4l2_subdev *sd, int on)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

return 0;

}

static int adv7282m_s_stream(struct v4l2_subdev *sd, int enable)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

u8 data;

dev_dbg(sd->dev, "%s\n", __func__);

if (enable) {

if (!adv7282m_data->running) {

/* Enable CSI output */

/*adv7282m_write_reg(adv7282m_data, 0xFF, 0x05);

data = adv7282m_read_reg(adv7282m_data, 0x00);

data &= ~0x80;

adv7282m_write_reg(adv7282m_data, 0x00, data);*/

}

adv7282m_data->running++;

} else {

if (adv7282m_data->running) {

/* Disable CSI Output */

/*adv7282m_write_reg(adv7282m_data, 0xFF, 0x05);

data = adv7282m_read_reg(adv7282m_data, 0x00);

data |= 0x80;

adv7282m_write_reg(adv7282m_data, 0x00, data);*/

}

adv7282m_data->running--;

}

return 0;

}

static int adv7282m_link_setup(struct media_entity *entity,

const struct media_pad *local,

const struct media_pad *remote, u32 flags)

{

return 0;

}

static const struct v4l2_subdev_pad_ops adv7282m_pad_ops = {

.enum_mbus_code = adv7282m_enum_mbus_code,

.enum_frame_size = adv7282m_enum_framesizes,

.enum_frame_interval = adv7282m_enum_frame_interval,

.get_fmt = adv7282m_get_fmt,

.set_fmt = adv7282m_set_fmt,

.get_frame_desc = adv7282m_get_frame_desc,

.set_frame_desc = adv7282m_set_frame_desc,

};

static const struct v4l2_subdev_core_ops adv7282m_core_ops = {

.s_power = adv7282m_set_power,

};

static const struct v4l2_subdev_video_ops adv7282m_video_ops = {

.g_std = adv7282m_g_std,

.s_parm = adv7282m_s_parm,

.g_parm = adv7282m_g_parm,

.s_stream = adv7282m_s_stream,

};

static const struct v4l2_subdev_ops adv7282m_subdev_ops = {

.core = &adv7282m_core_ops,

.pad = &adv7282m_pad_ops,

.video = &adv7282m_video_ops,

};

static const struct media_entity_operations adv7282m_sd_media_ops = {

.link_setup = adv7282m_link_setup,

};

static ssize_t adv7282_attr_show(struct kobject *kobj, struct kobj_attribute *attr, char *buf)

{

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

return 0;//sprintf(buf, "%d\n", adv7282_status);

}

static struct kobj_attribute adv7282_attribute = __ATTR(adv7282_attr, 0444, adv7282_attr_show, NULL);

/*!

* adv7282m I2C probe function

*

* @param adapter struct i2c_adapter *

* @return Error code indicating success or failure

*/

static int adv7282m_probe(struct i2c_client *client,

const struct i2c_device_id *id)

{

struct device *dev = &client->dev;

struct sensor_data *adv7282m_data;

struct v4l2_subdev *sd;

u8 data;

int retval;

int ret;

unsigned long irq_flags;

printk("[lee][%s:--%s]--%d\n", __FILE__, __func__, __LINE__);

adv7282m_data = devm_kzalloc(dev, sizeof(*adv7282m_data), GFP_KERNEL);

if (!adv7282m_data)

return -ENOMEM;

/* request reset pin */

adv7282m_data->rst_gpio = of_get_named_gpio(dev->of_node, "rst-gpios", 0);

if (!gpio_is_valid(adv7282m_data->rst_gpio)) {

dev_err(dev, "no sensor reset pin available\n");

return -ENODEV;

}

retval = devm_gpio_request_one(dev, adv7282m_data->rst_gpio, GPIOF_OUT_INIT_HIGH,

"adv7282m_rst");

if (retval < 0)

return retval;

/*msleep(5);

gpio_direction_output(adv7282m_data->rst_gpio, 0);

printk("lee >>>>>>%s %d\n", __FUNCTION__, __LINE__);

msleep(5);

gpio_direction_output(adv7282m_data->rst_gpio, 1);

printk("lee >>>>>>%s %d\n", __FUNCTION__, __LINE__);

msleep(5);*/

/* request power down pin */

adv7282m_data->pwn_gpio = of_get_named_gpio(dev->of_node, "pwn-gpios", 0);

if (!gpio_is_valid(adv7282m_data->pwn_gpio)) {

dev_err(dev, "no sensor pwdn pin available\n");

return -ENODEV;

}

retval = devm_gpio_request_one(dev, adv7282m_data->pwn_gpio, GPIOF_OUT_INIT_HIGH,

"adv7282m_pwd");

if (retval < 0)

return retval;

adv7282m_data->num_lanes = 1; /* Default 2 lanes */

of_property_read_u32(dev->of_node, "data-lanes", &adv7282m_data->num_lanes);

adv7282m_hw_reset(adv7282m_data);

mutex_init(&adv7282m_data->adv7282_lock);

adv7282m_data->i2c_client = client;

adv7282m_data->video_id = NTSC;

adv7282m_data->format.code = MEDIA_BUS_FMT_YUYV8_1X16;

adv7282m_data->format.width = video_fmts[adv7282m_data->video_id].width;

adv7282m_data->format.height = video_fmts[adv7282m_data->video_id].height;

adv7282m_data->format.colorspace = V4L2_COLORSPACE_JPEG;

/*****************************************

* Pass mipi phy clock rate Mbps

* fcsi2 = PCLk * WIDTH * CHANNELS / LANES

* fsci2 = 27MPCLK * 8 bit * 4 channels / num_lanes

****************************************/

adv7282m_data->format.reserved[0] = 27 * 8 * 1 / adv7282m_data->num_lanes;

adv7282m_data->format.field = V4L2_FIELD_INTERLACED;

adv7282m_data->streamcap.capturemode = 0;

adv7282m_data->streamcap.timeperframe.denominator = video_fmts[adv7282m_data->video_id].frame_rate;

adv7282m_data->streamcap.timeperframe.numerator = 1;

adv7282m_data->is_mipi = 1;

printk("lee 1+++++++++++++++++++++++++++++++++\n");

/* adv7282m read self ID. */

data = adv7282m_read_reg(adv7282m_data, ADV7282M_IDENT);

if (data < 0 || data != 0x43) {

printk("adv7282m camera is not found,ret:%x\n", data);

return -ENODEV;

}

printk("lee 2+++++++++++++++++++++++++++++++++\n");

adv7282m_data->chip_id = data;

adv7282m_data->streamcap.capability = V4L2_CAP_TIMEPERFRAME;

adv7282m_data->streamcap.timeperframe.denominator = 30;

adv7282m_data->streamcap.timeperframe.numerator = 1;

adv7282m_data->v_channel = 0;

sd = &adv7282m_data->subdev;

v4l2_i2c_subdev_init(sd, client, &adv7282m_subdev_ops);

sd->flags |= V4L2_SUBDEV_FL_HAS_DEVNODE;

sd->entity.function = MEDIA_ENT_F_CAM_SENSOR;

adv7282m_data->pads[MIPI_CSI2_SENS_VC0_PAD_SOURCE].flags = MEDIA_PAD_FL_SOURCE;

ret = media_entity_pads_init(&sd->entity, MIPI_CSI2_SENS_VCX_PADS_NUM,

adv7282m_data->pads);

if (retval < 0)

return retval;

adv7282m_data->subdev.entity.ops = &adv7282m_sd_media_ops;

retval = v4l2_async_register_subdev(&adv7282m_data->subdev);

if (retval < 0) {

dev_err(&client->dev,

"%s--Async register failed, ret=%d\n", __func__, retval);

media_entity_cleanup(&sd->entity);

}

printk("lee 3+++++++++++++++++++++++++++++++++\n");

retval = adv7282m_hardware_init(adv7282m_data);

if (retval < 0) {

dev_err(&client->dev, "camera init failed\n");

//clk_disable_unprepare(adv7282m_data->sensor_clk);

media_entity_cleanup(&sd->entity);

v4l2_async_unregister_subdev(sd);

return retval;

}

printk("lee 4+++++++++++++++++++++++++++++++++\n");

adv7282m_data->client_csi_tx = i2c_new_dummy(client->adapter, 0x44);

if (!adv7282m_data->client_csi_tx) {

return -ENOMEM;

}

adv7282m_data->client_csi_i2p = i2c_new_dummy(client->adapter, 0x42);

if (!adv7282m_data->client_csi_i2p) {

return -ENOMEM;

}

printk("lee 5+++++++++++++++++++++++++++++++++\n");

//Program Virtual Channel #1 under ADV7282-m

adv7282m_csi_write(adv7282m_data, 0x0D,0x40);

printk("lee 11111111111111111\n");

adv7282m_vpp_write(adv7282m_data,0xA3,0x00); //ADI Required Write

adv7282m_vpp_write(adv7282m_data,0x5B,0x00); //I2C_DEINT_ENABLE : Advanced Timing Enabled

adv7282m_vpp_write(adv7282m_data,0x55,0x80); //ADV_TIMING_ MODE_EN : Enable I2P / Enable the Deinterlacer for I2P

// adv7282m_vpp_write(adv7282m_data,0xA3,0x00); //ADI Required Write

printk("lee 3 1 ............\n");

adv7282m_csi_write(adv7282m_data, 0x01, 0x20);

adv7282m_csi_write(adv7282m_data, 0x02, 0x28);

adv7282m_csi_write(adv7282m_data, 0x03, 0x38);

adv7282m_csi_write(adv7282m_data, 0x04, 0x30);

adv7282m_csi_write(adv7282m_data, 0x05, 0x30);

adv7282m_csi_write(adv7282m_data, 0x06, 0x80);

adv7282m_csi_write(adv7282m_data, 0x07, 0x70);

adv7282m_csi_write(adv7282m_data, 0x08, 0x50);

printk("lee 3 2 ............\n");

adv7282m_csi_write(adv7282m_data, 0xDE, 0x02);

adv7282m_csi_write(adv7282m_data, 0xD2, 0xF7);

adv7282m_csi_write(adv7282m_data, 0xD8, 0x65);

adv7282m_csi_write(adv7282m_data, 0xE0, 0x09);

adv7282m_csi_write(adv7282m_data, 0x2C, 0x00);

adv7282m_csi_write(adv7282m_data, 0x1D, 0x80);

adv7282m_csi_write(adv7282m_data, 0x00, 0x00);

printk("lee 3 ............\n");

// CSI Initialisations provided by Analog Device

/* adv7282m_csi_write(adv7282m_data, 0xDE,0x02); //DPHY_PWDN_CTL : Power up MIPI D-PHY

printk("lee 4 ............\n");

adv7282m_csi_write(adv7282m_data, 0xD2,0xF7); //ADI Required Write

printk("lee 5 ............\n");

adv7282m_csi_write(adv7282m_data, 0xD8,0x65); //ADI Required Write

printk("lee 6 ............\n");

adv7282m_csi_write(adv7282m_data, 0xE0,0x09); //ADI Required Write

printk("lee 7 ............\n");

adv7282m_csi_write(adv7282m_data, 0x2C,0x00); //ADI Required Write

printk("lee 8 ............\n");

adv7282m_csi_write(adv7282m_data, 0x00,0x00); //Power up MIPI CSI-2 Tx --done--

printk("lee 9 ............\n");

*/

/* adv7282m request irq. */

/*irq_flags = irqd_get_trigger_type(irq_get_irq_data(client->irq));

irq_flags |= IRQF_ONESHOT;

if (client->irq) {

ret = request_threaded_irq(client->irq, NULL, adv7282_isr, irq_flags,

"adv7282m_irq", adv7282m_data);

if (ret < 0) {

pr_err("adv7282m request irq fail,ret:%x\n",ret);

return ret;

}

}*/

/* adv7282m request irq end. */

/* Create sys file point. */

/*ret = sysfs_create_file(&client->dev.kobj, &adv7282_attribute.attr);

if(ret) {

pr_err("adv7282m sysfs_create_file fail,ret:%x\n",ret);

return ret;

}*/

/* Create sys file point end. */

/* Disable CSI Output */

// Page 5

adv7282m_data->running = 0;

dev_info(&adv7282m_data->i2c_client->dev,

"adv7282m is found, id = 0x%x, name %s\n", adv7282m_data->chip_id, sd->name);

return retval;

}

/*!

* adv7282m I2C detach function

*

* @param client struct i2c_client *

* @return Error code indicating success or failure

*/

static int adv7282m_remove(struct i2c_client *client)

{

struct v4l2_subdev *sd = i2c_get_clientdata(client);

struct sensor_data *adv7282m_data = subdev_to_sensor_data(sd);

clk_disable_unprepare(adv7282m_data->sensor_clk);

media_entity_cleanup(&sd->entity);

v4l2_async_unregister_subdev(sd);

return 0;

}

static const struct i2c_device_id adv7282m_id[] = {

{"adv7180_decoder", 0},

};

MODULE_DEVICE_TABLE(i2c, adv7282m_id);

static const struct of_device_id adv7282m_of_match[] = {

{ .compatible = "adv,adv7180_decoder" },

{ /* sentinel */ }

};

static struct i2c_driver adv7282m_i2c_driver = {

.driver = {

.owner = THIS_MODULE,

.name = "adv7180_decoder",

.of_match_table = of_match_ptr(adv7282m_of_match),

},

.probe = adv7282m_probe,

.remove = adv7282m_remove,

.id_table = adv7282m_id,

};

module_i2c_driver(adv7282m_i2c_driver);

MODULE_AUTHOR("NXP Semiconductor, Inc.");

MODULE_DESCRIPTION("adv7282m Video Decoder Driver");

MODULE_LICENSE("GPL");

MODULE_VERSION("1.0");

MODULE_ALIAS("CSI");

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

For iMX8MQ, you should reference to this driver, the iMX8MQ CSI is the updated version of IMX6UL CSI, they are using the same driver in kernel:

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi:

Click on the website ,Prompt unauthorized !

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Qiang Li:

I also need this patch file and documentation, thank you! My email is 542270618@qq.com

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

The document in "https://community.nxp.com/docs/DOC-330092 " is opened now. You can check it.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Qiang Li:

Dose imx8mq support support TVin architecture? and if yes, which de-interlace modes are supported, both weaving mode de-interlace or blending mode?

Does your patch above of ISL79987&adv7180_reference_driver_for_iMX8QXP.7z.zip can be ported to imx8mq, too?

And, whether imx8mq does support TV-in driver of TW9992 mipi ? Could you give the example for it?

Thanks!

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Qiang Li:

Inherited above post, correct SoC board is "imx8qm" not imx8mq.

And, add more two questions.

Question 1 : I port your binary tool mx8_v4l2_cap_drm to our imx8qm android 9 board, and I run as the command of "mx8_v4l2_cap_drm -cam 1 -d "/dev/video1" -fmt YUYV -num 30000 -log 6", which /dev/video1 is our video-in TW9992 MIPI driver, but get error code as below,

(init_video_channel:503): init channel[0] v4l2_dev_name=/dev[ 183.913165] mxc-isi 58140000.isi: mxc_isi_capture_open, ISI4

/video1 w/h=(1280,800)

(open_drm_device:611): Open /dev[ 183.924675] tw9992_s_power#1006: on=1

/dri/card0 success

(open_v4l2_device:644): open /dev/video1 success

========================================================

command pid dev master a uid magic[ 183.984317] mxc-isi 58140000.isi: mxc_isi_capture_release

composer@2.1-se 3628 0 y y 1000 0

[ 183.998481] tw9992_s_power#1006: on=0

composer@2.1-se 3628 128 n n 1000 0

mx8_v4l2_cap_dr 4909 0 n y 0 0

========================================================

Please ensure there is no other master client

========================================================

How can I fix it ?

Question 2: I use "v4l2-ctrl" to dump frame of tw9992, but get incorrect frame captured.

command:

v4l2-ctl -d /dev/video1 --set-standard=pal --set-fmt-video=width=720,height=576,pixelformat=YUYV --stream-mmap=3 --stream-skip=3 --stream-to=/sdcard/tw9992.raw --stream-count=1 --stream-poll

log:

[ 1168.781924] init: couldn't write 5757 to /dev/cpuset/camera-daemon/tasks: No such file or directory

[ 1168.924382] mxc-jpeg 58450000.jpegenc: Descriptor for dec/enc: ffff00000aa3f000 0xae002000

[ 1168.932948] mxc-jpeg 58450000.jpegenc: Descriptor for config phase: ffff00000aa40000 0xae003000

[ 1168.941737] mxc-jpeg 58450000.jpegenc: Configuration stream: ffff00000aa41000 0xae004000

[ 1168.951906] mxc-isi 58140000.isi: mxc_isi_capture_open, ISI4

[ 1168.957915] tw9992_s_power#1006: on=1

[ 1168.961974] mxc-isi 58140000.isi: mxc_isi_capture_release

[ 1168.972424] tw9992_s_power#1006: on=0

[ 1168.976346] mxc-isi 58100000.isi: mxc_isi_m2m_open, ISI0

[ 1168.987185] mxc-isi 58100000.isi: mxc_isi_m2m_release

[ 1168.999270] mxc-jpeg 58400000.jpegdec: Descriptor for dec/enc: ffff00000aa3f000 0xae002000

[ 1169.007593] mxc-jpeg 58400000.jpegdec: Descriptor for config phase: ffff00000aa40000 0xae003000

[ 1169.016352] mxc-jpeg 58400000.jpegdec: Configuration stream: ffff00000aa41000 0xae004000

[ 1169.032970] init: Service 'vendor.camera-provider-2-4' (pid 5757) exited with status 1

[ 1169.041114] init: Sending signal 9 to service 'vendor.camera-provider-2-4' (pid 5757) process group...

[ 1169.050649] audit: audit_lost=17678 audit_rate_limit=5 audit_backlog_limit=64

[ 1169.057950] audit: rate limit exceeded

[ 1169.061876] libprocessgroup: Successfully killed process cgroup uid 1047 pid 5757 in 11ms

[ 1169.146907] mxc-isi 58140000.isi: mxc_isi_capture_open, ISI4

[ 1169.152893] tw9992_s_power#1006: on=1

[ 1169.157024] mxc-isi 58140000.isi: mxc_isi_cap_s_std

[ 1169.161963] mxc-mipi-csi2 58247000.csi: mipi_csi2_s_std

[ 1169.167254] tw9992_s_std#827: 0 others

Standard set to 000000ff[ 1169.171157] mxc-isi 58140000.isi: mxc_isi_cap_g_fmt_mplane

[ 1169.178831] mxc-isi 58140000.isi: mxc_isi_cap_s_fmt_mplane, fmt=0x56595559

[ 1169.187645] mxc-isi 58140000.isi: cap_vb2_queue_setup, buf_n=3, size=829440

[ 1169.203720] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

[ 1169.209133] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

[ 1169.214559] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

[ 1169.219940] mxc-isi 58140000.isi: mxc_isi_cap_g_fmt_mplane

[ 1169.225487] mxc-isi 58140000.isi: mxc_isi_cap_streamon

[ 1169.230667] tw9992_set_fmt#905: mbusformat=0x1, pixelformat=0x50424752

[ 1169.237261] tw9992_get_fmt#968

[ 1169.240434] tw9992_mipi 7-0044: tw9992_get_fmt code=0x1017, w/h=(720,576), colorspace=7, field=0

[ 1169.249268] mxc-mipi-csi2 58247000.csi: width=720, height=576, fmt.code=0x1017

[ 1169.261526] input fmt RGB4

[ 1169.264255] output fmt YUYV

[ 1169.267092] mxc-isi 58140000.isi: mxc_isi_channel_set_scaling: no scale

[ 1169.273745] mxc-isi 58140000.isi: cap_vb2_start_streaming

[ 1169.282040] mxc-isi 58140000.isi: cap_vb2_start_streaming: num_plane=0 discard_size=829440 discard_buffer=ffff00002c8c5000

[ 1169.557859] mxc-isi 58140000.isi: ISI CHNLC register dump, isi4

[ 1169.563808] mxc-isi 58140000.isi: CHNL_CTRL 0x0h = 0xc0ff0003

[ 1169.571010] mxc-isi 58140000.isi: CHNL_IMG_CTRL 0x4h = 0x20000006

[ 1169.578007] mxc-isi 58140000.isi: CHNL_OUT_BUF_CTRL 0x8h = 0x c000

[ 1169.585182] mxc-isi 58140000.isi: CHNL_IMG_CFG 0xCh = 0x 24002d0

[ 1169.592182] mxc-isi 58140000.isi: CHNL_IER 0x10h = 0x3dff0000

[ 1169.599220] mxc-isi 58140000.isi: CHNL_STS 0x14h = 0x 200

[ 1169.606217] mxc-isi 58140000.isi: CHNL_SCALE_FACTOR 0x18h = 0x10001000

[ 1169.613239] mxc-isi 58140000.isi: CHNL_SCALE_OFFSET 0x1Ch = 0x 0

[ 1169.620245] mxc-isi 58140000.isi: CHNL_CROP_ULC 0x20h = 0x 0

[ 1169.627253] mxc-isi 58140000.isi: CHNL_CROP_LRC 0x24h = 0x 0

[ 1169.634243] mxc-isi 58140000.isi: CHNL_CSC_COEFF0 0x28h = 0x 810041

[ 1169.641258] mxc-isi 58140000.isi: CHNL_CSC_COEFF1 0x2Ch = 0x 7db0019

[ 1169.648259] mxc-isi 58140000.isi: CHNL_CSC_COEFF2 0x30h = 0x 7007b6

[ 1169.655266] mxc-isi 58140000.isi: CHNL_CSC_COEFF3 0x34h = 0x 7a20070

[ 1169.662262] mxc-isi 58140000.isi: CHNL_CSC_COEFF4 0x38h = 0x 1007ee

[ 1169.669274] mxc-isi 58140000.isi: CHNL_CSC_COEFF5 0x3Ch = 0x 800080

[ 1169.676265] mxc-isi 58140000.isi: CHNL_ROI_0_ALPHA 0x40h = 0x 0

[ 1169.683274] mxc-isi 58140000.isi: CHNL_ROI_0_ULC 0x44h = 0x 0

[ 1169.690264] mxc-isi 58140000.isi: CHNL_ROI_0_LRC 0x48h = 0x 0

[ 1169.697275] mxc-isi 58140000.isi: CHNL_ROI_1_ALPHA 0x4Ch = 0x 0

[ 1169.704275] mxc-isi 58140000.isi: CHNL_ROI_1_ULC 0x50h = 0x 0

[ 1169.711286] mxc-isi 58140000.isi: CHNL_ROI_1_LRC 0x54h = 0x 0

[ 1169.718276] mxc-isi 58140000.isi: CHNL_ROI_2_ALPHA 0x58h = 0x 0

[ 1169.725286] mxc-isi 58140000.isi: CHNL_ROI_2_ULC 0x5Ch = 0x 0

[ 1169.732294] mxc-isi 58140000.isi: CHNL_ROI_2_LRC 0x60h = 0x 0

[ 1169.739304] mxc-isi 58140000.isi: CHNL_ROI_3_ALPHA 0x64h = 0x 0

[ 1169.746294] mxc-isi 58140000.isi: CHNL_ROI_3_ULC 0x68h = 0x 0

[ 1169.753308] mxc-isi 58140000.isi: CHNL_ROI_3_LRC 0x6Ch = 0x 0

[ 1169.760310] mxc-isi 58140000.isi: CHNL_OUT_BUF1_ADDR_Y 0x70h = 0xbfa00000

[ 1169.767317] mxc-isi 58140000.isi: CHNL_OUT_BUF1_ADDR_U 0x74h = 0x 0

[ 1169.774304] mxc-isi 58140000.isi: CHNL_OUT_BUF1_ADDR_V 0x78h = 0x 0

[ 1169.781315] mxc-isi 58140000.isi: CHNL_OUT_BUF_PITCH 0x7Ch = 0x 5a0

[ 1169.788308] mxc-isi 58140000.isi: CHNL_IN_BUF_ADDR 0x80h = 0x 0

[ 1169.795316] mxc-isi 58140000.isi: CHNL_IN_BUF_PITCH 0x84h = 0x 0

[ 1169.802306] mxc-isi 58140000.isi: CHNL_MEM_RD_CTRL 0x88h = 0x 0

[ 1169.809317] mxc-isi 58140000.isi: CHNL_OUT_BUF2_ADDR_Y 0x8Ch = 0xbf700000

[ 1169.816317] mxc-isi 58140000.isi: CHNL_OUT_BUF2_ADDR_U 0x90h = 0x 0

[ 1169.823329] mxc-isi 58140000.isi: CHNL_OUT_BUF2_ADDR_V 0x94h = 0x 0

[ 1169.830325] tw9992_s_stream#990: enable=1

[ 1169.834376] tw9992_start_mipi#589

[ 1169.838458] tw9992_check_stable_decoder use 00ms

[ 1169.870957] mxc-mipi-csi2 58247000.csi: mipi_csi2_s_stream: 1, csi2dev: 0x0

[ 1169.877993] tw9992_get_fmt#968

[ 1169.881056] tw9992_mipi 7-0044: tw9992_get_fmt code=0x1017, w/h=(720,576), colorspace=7, field=0

[ 1169.890324] mxc-mipi-csi2 58247000.csi: width=720, height=576, fmt.code=0x1017

[ 1169.897718] mxc-isi 58140000.isi: mxc_isi_pipeline_enable ,entity is no v4l2, mxc_isi.4.capture

[ 1169.933009] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

<[ 1169.953905] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

<[ 1169.972868] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

<[ 1170.010709] mxc-isi 58140000.isi: cap_vb2_buffer_prepare

<[ 1170.016104] mxc-isi 58140000.isi: mxc_isi_cap_streamoff

[ 1170.021730] tw9992_s_stream#990: enable=0

[ 1170.025774] tw9992_stop_mipi#578

[ 1170.030666] mxc-mipi-csi2 58247000.csi: mipi_csi2_s_stream: 0, csi2dev: 0x0

[ 1170.037735] mxc-isi 58140000.isi: mxc_isi_pipeline_enable ,entity is no v4l2, mxc_isi.4.capture

[ 1170.046954] mxc-isi 58140000.isi: cap_vb2_stop_streaming

[ 1170.052784] mxc-isi 58140000.isi: mxc_isi_capture_release

[ 1170.064182] tw9992_s_power#1006: on=0

frame captured:

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Qiang Li:

Append the log of dump register of mxc-mipi-csi2.c

[ 165.147668] MIPI CSI2 HC register dump, mipi csi1

[ 165.152422] MIPI CSI2 HC num of lanes 0x100 = 0x0

[ 165.157490] MIPI CSI2 HC dis lanes 0x104 = 0xe

[ 165.162582] MIPI CSI2 HC BIT ERR 0x108 = 0x0

[ 165.167656] MIPI CSI2 HC IRQ STATUS 0x10C = 0x8

[ 165.172740] MIPI CSI2 HC IRQ MASK 0x110 = 0x1ff

[ 165.177984] MIPI CSI2 HC ULPS STATUS 0x114 = 0x0

[ 165.183081] MIPI CSI2 HC DPHY ErrSotHS 0x118 = 0x0

[ 165.188160] MIPI CSI2 HC DPHY ErrSotSync 0x11c = 0x0

[ 165.193261] MIPI CSI2 HC DPHY ErrEsc 0x120 = 0x0

[ 165.198332] MIPI CSI2 HC DPHY ErrSyncEsc 0x124 = 0x0

[ 165.203425] MIPI CSI2 HC DPHY ErrControl 0x128 = 0x0

[ 165.208724] MIPI CSI2 HC DISABLE_PAYLOAD 0x12C = 0x0

[ 165.213835] MIPI CSI2 HC DISABLE_PAYLOAD 0x130 = 0x0

[ 165.218919] MIPI CSI2 HC IGNORE_VC 0x180 = 0x0

[ 165.224020] MIPI CSI2 HC VID_VC 0x184 = 0x0

[ 165.229101] MIPI CSI2 HC FIFO_SEND_LEVEL 0x188 = 0x0

[ 165.234232] MIPI CSI2 HC VID_VSYNC 0x18C = 0x0

[ 165.239329] MIPI CSI2 HC VID_SYNC_FP 0x190 = 0x0

[ 165.244424] MIPI CSI2 HC VID_HSYNC 0x194 = 0x0

[ 165.249509] MIPI CSI2 HC VID_HSYNC_BP 0x198 = 0x0

[ 165.254603] MIPI CSI2 CSR register dump

[ 165.258480] MIPI CSI2 CSR PLM_CTRL 0x000 = 0x801

[ 165.263761] MIPI CSI2 CSR PHY_CTRL 0x004 = 0x2000af

[ 165.269389] MIPI CSI2 CSR PHY_Status 0x008 = 0x1

[ 165.274512] MIPI CSI2 CSR PHY_Test_Status 0x010 = 0x0

[ 165.279599] MIPI CSI2 CSR PHY_Test_Status 0x014 = 0x0

[ 165.284694] MIPI CSI2 CSR PHY_Test_Status 0x018 = 0x0

[ 165.289775] MIPI CSI2 CSR PHY_Test_Status 0x01C = 0x0

[ 165.294873] MIPI CSI2 CSR PHY_Test_Status 0x020 = 0x0

[ 165.299962] MIPI CSI2 CSR VC Interlaced 0x030 = 0x0

[ 165.305071] MIPI CSI2 CSR Data Type Dis 0x038 = 0x0

[ 165.310162] MIPI CSI2 CSR 420 1st type 0x040 = 0x0

[ 165.315278] MIPI CSI2 CSR Ctr_Ck_Rst_Ctr 0x044 = 0x1

[ 165.320373] MIPI CSI2 CSR Stream Fencing 0x048 = 0x0

[ 165.325479] MIPI CSI2 CSR Stream Fencing 0x04C = 0x0

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

From your ISI dump log, your camera input is set to RGB4, that is not correct. And you had also enabled CSC, you'd better set to no CSC and re-scale, just capture the data into memory directly, then check if it can work or not.

[ 1169.261526] input fmt RGB4

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Register setting for MIPI CSI2 camera, input is UYVY NTSC format.

[ 51.328487] input fmt YUV4 = 720x480@30

[ 51.336847] output fmt YUYV

[ 51.675116] mxc_isi->deinterlace = 2.

[ 51.678880] mxc-isi 58100000.isi: ISI CHNLC register dump, isi0

[ 51.684852] mxc-isi 58100000.isi: CHNL_CTRL 0x0h = 0xe0ff0002

[ 51.691863] mxc-isi 58100000.isi: CHNL_IMG_CTRL 0x4h = 0x20002001

[ 51.698882] mxc-isi 58100000.isi: CHNL_OUT_BUF_CTRL 0x8h = 0x c000

[ 51.705890] mxc-isi 58100000.isi: CHNL_IMG_CFG 0xCh = 0x f002d0

[ 51.712904] mxc-isi 58100000.isi: CHNL_IER 0x10h = 0x3dff0000

[ 51.719909] mxc-isi 58100000.isi: CHNL_STS 0x14h = 0x 200

[ 51.726928] mxc-isi 58100000.isi: CHNL_SCALE_FACTOR 0x18h = 0x10001000

[ 51.733933] mxc-isi 58100000.isi: CHNL_SCALE_OFFSET 0x1Ch = 0x 0

[ 51.740948] mxc-isi 58100000.isi: CHNL_CROP_ULC 0x20h = 0x 0

[ 51.747952] mxc-isi 58100000.isi: CHNL_CROP_LRC 0x24h = 0x 0

[ 51.754972] mxc-isi 58100000.isi: CHNL_CSC_COEFF0 0x28h = 0x 0

[ 51.761959] mxc-isi 58100000.isi: CHNL_CSC_COEFF1 0x2Ch = 0x 0

[ 51.768966] mxc-isi 58100000.isi: CHNL_CSC_COEFF2 0x30h = 0x 0

[ 51.775966] mxc-isi 58100000.isi: CHNL_CSC_COEFF3 0x34h = 0x 0

[ 51.782985] mxc-isi 58100000.isi: CHNL_CSC_COEFF4 0x38h = 0x 0

[ 51.789996] mxc-isi 58100000.isi: CHNL_CSC_COEFF5 0x3Ch = 0x 0

[ 51.797001] mxc-isi 58100000.isi: CHNL_ROI_0_ALPHA 0x40h = 0x 0

[ 51.804001] mxc-isi 58100000.isi: CHNL_ROI_0_ULC 0x44h = 0x 0

[ 51.811020] mxc-isi 58100000.isi: CHNL_ROI_0_LRC 0x48h = 0x 0

[ 51.818013] mxc-isi 58100000.isi: CHNL_ROI_1_ALPHA 0x4Ch = 0x 0

[ 51.825016] mxc-isi 58100000.isi: CHNL_ROI_1_ULC 0x50h = 0x 0

[ 51.832016] mxc-isi 58100000.isi: CHNL_ROI_1_LRC 0x54h = 0x 0

[ 51.839028] mxc-isi 58100000.isi: CHNL_ROI_2_ALPHA 0x58h = 0x 0

[ 51.846023] mxc-isi 58100000.isi: CHNL_ROI_2_ULC 0x5Ch = 0x 0

[ 51.853031] mxc-isi 58100000.isi: CHNL_ROI_2_LRC 0x60h = 0x 0

[ 51.860024] mxc-isi 58100000.isi: CHNL_ROI_3_ALPHA 0x64h = 0x 0

[ 51.867047] mxc-isi 58100000.isi: CHNL_ROI_3_ULC 0x68h = 0x 0

[ 51.874039] mxc-isi 58100000.isi: CHNL_ROI_3_LRC 0x6Ch = 0x 0

[ 51.881039] mxc-isi 58100000.isi: CHNL_OUT_BUF1_ADDR_Y 0x70h = 0xa6a00000

[ 51.888032] mxc-isi 58100000.isi: CHNL_OUT_BUF1_ADDR_U 0x74h = 0x 0

[ 51.895054] mxc-isi 58100000.isi: CHNL_OUT_BUF1_ADDR_V 0x78h = 0x 0

[ 51.902056] mxc-isi 58100000.isi: CHNL_OUT_BUF_PITCH 0x7Ch = 0x 5a0

[ 51.909049] mxc-isi 58100000.isi: CHNL_IN_BUF_ADDR 0x80h = 0x 0

[ 51.916048] mxc-isi 58100000.isi: CHNL_IN_BUF_PITCH 0x84h = 0x 0

[ 51.923057] mxc-isi 58100000.isi: CHNL_MEM_RD_CTRL 0x88h = 0x 0

[ 51.930056] mxc-isi 58100000.isi: CHNL_OUT_BUF2_ADDR_Y 0x8Ch = 0xa6700000

[ 51.937153] mxc-isi 58100000.isi: CHNL_OUT_BUF2_ADDR_U 0x90h = 0x 0

[ 51.944152] mxc-isi 58100000.isi: CHNL_OUT_BUF2_ADDR_V 0x94h = 0x 0

[ 51.951140] mxc-isi 58100000.isi: CHNL_SCL_IMG_CFG 0x98h = 0x f002d0

[ 51.959675] mxc_csi2_get_sensor_fmt: hs_settle = 0xa.

[ 51.964891] mxc_csi2_get_sensor_fmt: tvdec = 4.

[ 51.969565] MIPI CSI2 HC register dump, mipi csi0

[ 51.974371] MIPI CSI2 HC num of lanes 0x100 = 0x1

[ 51.979449] MIPI CSI2 HC dis lanes 0x104 = 0xc

[ 51.984529] MIPI CSI2 HC BIT ERR 0x108 = 0x0

[ 51.992557] MIPI CSI2 HC IRQ STATUS 0x10C = 0x8

[ 51.997629] MIPI CSI2 HC IRQ MASK 0x110 = 0x1ff

[ 52.002878] MIPI CSI2 HC ULPS STATUS 0x114 = 0x0

[ 52.007957] MIPI CSI2 HC DPHY ErrSotHS 0x118 = 0x0

[ 52.013021] MIPI CSI2 HC DPHY ErrSotSync 0x11c = 0x0

[ 52.018086] MIPI CSI2 HC DPHY ErrEsc 0x120 = 0x0

[ 52.023208] MIPI CSI2 HC DPHY ErrSyncEsc 0x124 = 0x0

[ 52.028289] MIPI CSI2 HC DPHY ErrControl 0x128 = 0x0

[ 52.033387] MIPI CSI2 HC DISABLE_PAYLOAD 0x12C = 0x0

[ 52.038462] MIPI CSI2 HC DISABLE_PAYLOAD 0x130 = 0x0

[ 52.043541] MIPI CSI2 HC IGNORE_VC 0x180 = 0x0

[ 52.048604] MIPI CSI2 HC VID_VC 0x184 = 0x0

[ 52.053670] MIPI CSI2 HC FIFO_SEND_LEVEL 0x188 = 0x0

[ 52.058735] MIPI CSI2 HC VID_VSYNC 0x18C = 0x0

[ 52.063806] MIPI CSI2 HC VID_SYNC_FP 0x190 = 0x0

[ 52.068874] MIPI CSI2 HC VID_HSYNC 0x194 = 0x0

[ 52.073938] MIPI CSI2 HC VID_HSYNC_BP 0x198 = 0x0

[ 52.079002] MIPI CSI2 CSR register dump

[ 52.082851] MIPI CSI2 CSR PLM_CTRL 0x000 = 0x801

[ 52.088095] MIPI CSI2 CSR PHY_CTRL 0x004 = 0x2000af

[ 52.093598] MIPI CSI2 CSR PHY_Status 0x008 = 0x1

[ 52.098662] MIPI CSI2 CSR PHY_Test_Status 0x010 = 0x0

[ 52.103728] MIPI CSI2 CSR PHY_Test_Status 0x014 = 0x0

[ 52.108798] MIPI CSI2 CSR PHY_Test_Status 0x018 = 0x0

[ 52.113866] MIPI CSI2 CSR PHY_Test_Status 0x01C = 0x0

[ 52.118939] MIPI CSI2 CSR PHY_Test_Status 0x020 = 0x0

[ 52.124005] MIPI CSI2 CSR VC Interlaced 0x030 = 0xf

[ 52.129068] MIPI CSI2 CSR Data Type Dis 0x038 = 0x0

[ 52.134133] MIPI CSI2 CSR 420 1st type 0x040 = 0x0

[ 52.139198] MIPI CSI2 CSR Ctr_Ck_Rst_Ctr 0x044 = 0x1

[ 52.144264] MIPI CSI2 CSR Stream Fencing 0x048 = 0x0

[ 52.149328] MIPI CSI2 CSR Stream Fencing 0x04C = 0x0

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Qiang,

We have two MIPI CSI2 devices in our HW board,

one is camera sensor OV5640 used ISI.0 (mxc-isi 58100000.isi), and

the another is video-in TW9992 used ISI.4 (mxc-isi 58140000.isi).

Now, in our bsp ROM, camera OV5460 is ok, can see camera preview screen and can take picture, can record video, it works normally.

However, video-in TW9992 is not ok, I use "v4l2-ctrl" command-line tool to dump frame of tw9992, but get incorrect frame captured.

Below links are the registers dumped of both OV5640 and TW9992.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi ting sung

From your tw9992 register dump, you haven't enabled de-interlace, if so, the TW9992 PAL signal should be handled as 720*288@50fps UYVY camera.

I think you can disable the OV5640 first (make it no MIPI CSI2 output), just debug the TW9992 only.

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Qiang Li

Here is my environment

HW platform: imx8-qm, tw9992

OS: Yocto Linux

Here is my CSI setting

[ 9.889110] mx8-img-md: Registered mxc_isi.0.capture as /dev/video0

[ 9.895494] mx8-img-md: Registered mxc_isi.4.capture as /dev/video1

[ 9.901869] mxc-isi 58140000.isi: register m2m device success

[ 9.907732] mx8-img-md: Registered sensor subdevice: tw9992_mipi 11-0044 (1)

[ 9.914798] mx8-img-md: mxc_md_create_links 119created link [mxc_isi.0] => [mxc_isi.0.capture]

[ 9.923424] mx8-img-md: mxc_md_create_links 232created link [mxc-mipi-csi2.0] => [mxc_isi.0]

[ 9.931874] mx8-img-md: mxc_md_create_links 119created link [mxc_isi.4] => [mxc_isi.4.capture]

[ 9.940499] mx8-img-md: mxc_md_create_links 232created link [mxc-mipi-csi2.1] => [mxc_isi.4]

[ 9.948944] tw9992_link_setup#1339

[ 9.952354] mx8-img-md: mxc_md_create_links 309 created link [tw9992_mipi 11-0044] => [mxc-mipi-csi2.1]

I run ./mx8_v4l2_cap_drm.out -cam 1 -d "/dev/video1" -fmt YUYV of

Get a file as a normal preview

But run ./mx8_v4l2_cap_drm.out -cam 1 -d "/dev/video1" -fmt YUYV

Get a color issue preview

Is this color issue about blending or weaving mode setting ?

Can you provide some suggestions ?

Thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Simon Lin ,

The default "mx8_v4l2_cap_drm.out " can't support YUYV render to DRM display, so I attched the modified application for YUYV render:

2019-11-14 update:

Add the test application "mx8_v4l2_cap_drm.tar.gz" to support YUYV render to display.

Test command to render 4 weaving mode cameras:

./mx8_v4l2_cap_drm.out -cam 0x1 -fmt YUYV -num 30000

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Qiang Li

Thanks for your advice, it's helpful

The TV function works , but I get a new issue

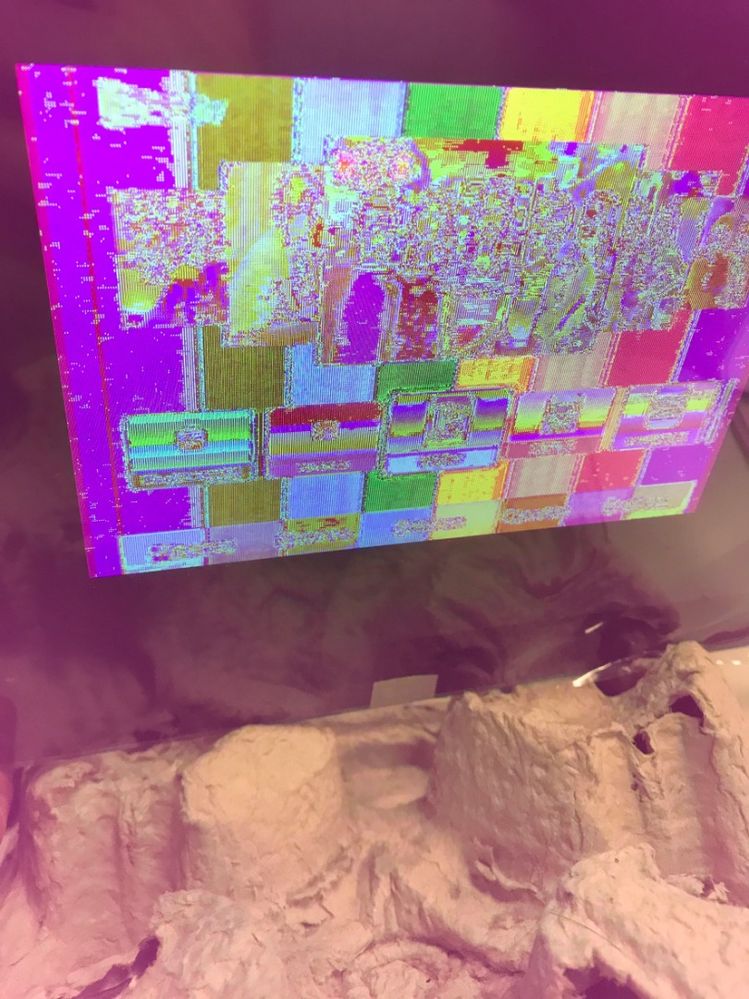

There is interlace section When switch TV page like below photo

I set weaving mode de-interlace in CHNL_IMG_CTRL_DEINT_WEAVE_ODD_EVEN

Should I change to blending mode ?

Can you provide some suggestions ?

Thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Hi Qiang Li

I intergrate blending mode on ISI4 to support tw9992

But it doesn't work to display

This is my isi4 register dump log

How can I fix it ?

Thanks

[ 92.772953] ---> mxc_isi_capture_open , mxc_isi->id = 4

[ 92.779344] ---> mxc_isi_get_remote_source_pad

[ 92.784548] ---> tw9992_s_power

[ 92.787917] --->mxc_isi_capture_open mxc_isi->blending 1

[ 93.098117] ---> mxc_isi_cap_enum_framesizes

[ 93.102503] ---> mxc_isi_find_format

[ 93.106517] ---> mxc_isi_get_remote_source_pad

[ 93.111008] ---> tw9992_enum_framesizes

[ 93.115042] ---> mxc_isi_cap_s_parm

[ 93.118760] ---> mxc_isi_get_remote_source_pad

[ 93.123407] ---> tw9992_s_parm

[ 93.126492] ---> mxc_isi_cap_s_fmt_mplane

[ 93.137216] ---> cap_vb2_queue_setup

[ 93.140969] ---> mxc_isi_cap_streamon

[ 93.144707] ---> mxc_isi_config_parm

[ 93.148311] ---> mxc_isi_source_fmt_init

[ 93.153146] ---> mxc_isi_get_remote_source_pad

[ 93.161351] ---> tw9992_set_fmt

[ 93.164549] ---> tw9992_stop_mipi

[ 93.170939] ---> tw9992_start_mipi

[ 93.174356] ---> tw9992_check_stable_decoder

[ 93.212088] ---> tw9992_get_fmt

[ 93.215288] ---> mxc_isi_get_src_fmt

[ 93.219008] --->mxc_isi_channel_set_deinterlace mxc_isi->blending 1

[ 93.225436] --->mxc_isi_channel_weaving_config mxc_isi->blending 1

[ 93.237374] --->mxc_isi_config_parm mxc_isi->blending 1

[ 93.251593] bypass csc

[ 93.255019] input fmt YUV4

[ 93.258612] output fmt YUYV

[ 93.261488] --->mxc_isi_channel_config mxc_isi->blending 1

[ 93.267046] ---> cap_vb2_start_streaming

[ 93.273126] --->mxc_isi_channel_enable mxc_isi->blending 1

[ 93.562981] ISI CHNLC register dump, isi4

[ 93.567042] CHNL_CTRL 0x0h = 0xc0ff0015

[ 93.572483] CHNL_IMG_CTRL 0x4h = 0x20000009

[ 93.577601] CHNL_OUT_BUF_CTRL 0x8h = 0x 8000

[ 93.582719] CHNL_IMG_CFG 0xCh = 0x 1e002d0

[ 93.587897] CHNL_IER 0x10h = 0x3dff0000

[ 93.593037] CHNL_STS 0x14h = 0x 200

[ 93.598139] CHNL_SCALE_FACTOR 0x18h = 0x10001000

[ 93.603247] CHNL_SCALE_OFFSET 0x1Ch = 0x 8000000

[ 93.608337] CHNL_CROP_ULC 0x20h = 0x 0

[ 93.613619] type=1400 audit(6177983976.060:6592): avc: denied { dac_read_search } for pid=5248 comm="main" capability=2 scontext=u:r:zygote:s0 tcontext=u:r:zygote:s0 tclass=capability permissive=0

[ 93.615044] CHNL_CROP_LRC 0x24h = 0x 0

[ 93.632089] type=1400 audit(6177983977.776:6604): avc: denied { dac_read_search } for pid=5330 comm="main" capability=2 scontext=u:r:zygote:s0 tcontext=u:r:zygote:s0 tclass=capability permissive=0

[ 93.636256] CHNL_CSC_COEFF0 0x28h = 0x 0

[ 93.636261] CHNL_CSC_COEFF1 0x2Ch = 0x 0

[ 93.636264] CHNL_CSC_COEFF2 0x30h = 0x 0

[ 93.636267] CHNL_CSC_COEFF3 0x34h = 0x 0

[ 93.636281] CHNL_CSC_COEFF4 0x38h = 0x 0

[ 93.679935] CHNL_CSC_COEFF5 0x3Ch = 0x 0

[ 93.685086] CHNL_ROI_0_ALPHA 0x40h = 0x 0

[ 93.690165] CHNL_ROI_0_ULC 0x44h = 0x 0

[ 93.695268] CHNL_ROI_0_LRC 0x48h = 0x 0

[ 93.700360] CHNL_ROI_1_ALPHA 0x4Ch = 0x 0

[ 93.705480] CHNL_ROI_1_ULC 0x50h = 0x 0

[ 93.710564] CHNL_ROI_1_LRC 0x54h = 0x 0

[ 93.715658] CHNL_ROI_2_ALPHA 0x58h = 0x 0

[ 93.720737] CHNL_ROI_2_ULC 0x5Ch = 0x 0

[ 93.725843] CHNL_ROI_2_LRC 0x60h = 0x 0

[ 93.730923] CHNL_ROI_3_ALPHA 0x64h = 0x 0

[ 93.736010] CHNL_ROI_3_ULC 0x68h = 0x 0

[ 93.741089] CHNL_ROI_3_LRC 0x6Ch = 0x 0

[ 93.746193] CHNL_OUT_BUF1_ADDR_Y 0x70h = 0xc1400000

[ 93.751267] CHNL_OUT_BUF1_ADDR_U 0x74h = 0x 0

[ 93.756355] CHNL_OUT_BUF1_ADDR_V 0x78h = 0x 0

[ 93.761450] CHNL_OUT_BUF_PITCH 0x7Ch = 0x 5a0

[ 93.766545] CHNL_IN_BUF_ADDR 0x80h = 0xc1200000

[ 93.771621] CHNL_IN_BUF_PITCH 0x84h = 0x 5a0

[ 93.776710] CHNL_MEM_RD_CTRL 0x88h = 0xd0000000

[ 93.781812] CHNL_OUT_BUF2_ADDR_Y 0x8Ch = 0xc0500000

[ 93.786951] CHNL_OUT_BUF2_ADDR_U 0x90h = 0x 0

[ 93.792042] CHNL_OUT_BUF2_ADDR_V 0x94h = 0x 0

[ 93.797541] --->mxc_isi_channel_enable mxc_isi->blending 1

[ 93.804152] ISI CHNLC register dump, isi4

[ 93.808246] CHNL_CTRL 0x0h = 0xc0ff0015

[ 93.813332] CHNL_IMG_CTRL 0x4h = 0x20000009

[ 93.818438] CHNL_OUT_BUF_CTRL 0x8h = 0x 8000

[ 93.823545] CHNL_IMG_CFG 0xCh = 0x 1e002d0

[ 93.828743] CHNL_IER 0x10h = 0x3dff0000

[ 93.833832] CHNL_STS 0x14h = 0x 200

[ 93.838938] CHNL_SCALE_FACTOR 0x18h = 0x10001000

[ 93.844019] CHNL_SCALE_OFFSET 0x1Ch = 0x 8000000

[ 93.849124] CHNL_CROP_ULC 0x20h = 0x 0

[ 93.854207] CHNL_CROP_LRC 0x24h = 0x 0

[ 93.859297] CHNL_CSC_COEFF0 0x28h = 0x 0

[ 93.864383] CHNL_CSC_COEFF1 0x2Ch = 0x 0

[ 93.869469] CHNL_CSC_COEFF2 0x30h = 0x 0

[ 93.874541] CHNL_CSC_COEFF3 0x34h = 0x 0

[ 93.879632] CHNL_CSC_COEFF4 0x38h = 0x 0

[ 93.884710] CHNL_CSC_COEFF5 0x3Ch = 0x 0

[ 93.889802] CHNL_ROI_0_ALPHA 0x40h = 0x 0

[ 93.894886] CHNL_ROI_0_ULC 0x44h = 0x 0

[ 93.899990] CHNL_ROI_0_LRC 0x48h = 0x 0

[ 93.905069] CHNL_ROI_1_ALPHA 0x4Ch = 0x 0

[ 93.910999] CHNL_ROI_1_ULC 0x50h = 0x 0

[ 93.916102] CHNL_ROI_1_LRC 0x54h = 0x 0

[ 93.921237] CHNL_ROI_2_ALPHA 0x58h = 0x 0

[ 93.926312] CHNL_ROI_2_ULC 0x5Ch = 0x 0

[ 93.931582] CHNL_ROI_2_LRC 0x60h = 0x 0

[ 93.936678] CHNL_ROI_3_ALPHA 0x64h = 0x 0

[ 93.941830] CHNL_ROI_3_ULC 0x68h = 0x 0

[ 93.947003] CHNL_ROI_3_LRC 0x6Ch = 0x 0

[ 93.952110] CHNL_OUT_BUF1_ADDR_Y 0x70h = 0xc1400000

[ 93.957200] CHNL_OUT_BUF1_ADDR_U 0x74h = 0x 0

[ 93.962307] CHNL_OUT_BUF1_ADDR_V 0x78h = 0x 0

[ 93.967396] CHNL_OUT_BUF_PITCH 0x7Ch = 0x 5a0

[ 93.972501] CHNL_IN_BUF_ADDR 0x80h = 0xc1200000

[ 93.977647] CHNL_IN_BUF_PITCH 0x84h = 0x 5a0

[ 93.982841] CHNL_MEM_RD_CTRL 0x88h = 0xd0000000

[ 93.987923] CHNL_OUT_BUF2_ADDR_Y 0x8Ch = 0xc0500000

[ 93.993039] CHNL_OUT_BUF2_ADDR_U 0x90h = 0x 0

[ 93.993846] audit: audit_lost=6452 audit_rate_limit=5 audit_backlog_limit=64

[ 93.998241] type=1400 audit(6177983977.776:6607): avc: denied { dac_read_search } for pid=5330 comm="main" capability=2 scontext=u:r:zygote:s0 tcontext=u:r:zygote:s0 tclass=capability permissive=0 duplicate messages suppressed

[ 93.998958] CHNL_OUT_BUF2_ADDR_V 0x94h = 0x 0

[ 93.998964] ---> mxc_isi_pipeline_enable

[ 93.998977] ---> tw9992_s_stream

[ 93.998981] ---> tw9992_start_mipi

[ 93.998984] ---> tw9992_check_stable_decoder

[ 94.005507] audit: rate limit exceeded

[ 94.025493] type=1400 audit(6177983978.156:6608): avc: denied { dac_read_search } for pid=5346 comm="main" capability=2 scontext=u:r:zygote:s0 tcontext=u:r:zygote:s0 tclass=capability permissive=0

[ 94.031961] tw9992_mipi Register Descriptions :

[ 94.072144] tw9992_mipi PRODUCT ID CODE REGISTER (ID) 0x00 = 0x 92

[ 94.083533] tw9992_mipi PRODUCT REVISION CODE REGISTER (ID) 0x01 = 0x 0

[ 94.094240] tw9992_mipi INPUT FORMAT (INFORM) 0x02 = 0x 40

[ 94.104847] tw9992_mipi DECODER STATUS REGISTER I (STATUS1) 0x03 = 0x 68

[ 94.115332] wm8960_mute set WM8960_CLOCK1

[ 94.119812] wm8960_mute set WM8960_CLOCK2

[ 94.128560] tw9992_mipi HSYNC DELAY CONTROL 0x04 = 0x 0

[ 94.139087] tw9992_mipi AFE SELECTION 0x05 = 0x 9

[ 94.149849] tw9992_mipi ANALOG CONTROL REGISTER (ACNTL) 0x06 = 0x 0

[ 94.161575] tw9992_mipi CROPPING REGISTER, HIGH (CROP_HI) 0x07 = 0x 2

[ 94.172354] tw9992_mipi VERTICAL DELAY REGISTER, LOW (VDELAY_LO) 0x08 = 0x 15

[ 94.183080] tw9992_mipi VERTICAL ACTIVE REGISTER, LOW (VACTIVE_LO) 0x09 = 0x f0

[ 94.193650] tw9992_mipi HORIZONTAL DELAY REGISTER, LOW (HDELAY_LO) 0x0A = 0x 12

[ 94.204839] tw9992_mipi HORIZONTAL ACTIVE REGISTER, LOW (HACTIVE_LO) 0x0B = 0x d0

[ 94.215455] tw9992_mipi CONTROL REGISTER I (CNTRL1) 0x0C = 0x cc

[ 94.226153] tw9992_mipi CC/WSS CONTROL 0x0D = 0x 0

[ 94.237241] tw9992_mipi BRIGHTNESS CONTROL REGISTER (BRIGHT) 0x10 = 0x 0

[ 94.247753] tw9992_mipi CONTRAST CONTROL REGISTER (CONTRAST) 0x11 = 0x 64

[ 94.258605] wm8960_mute set WM8960_CLOCK1

[ 94.263095] wm8960_mute set WM8960_CLOCK2

[ 94.271003] tw9992_mipi SHARPNESS CONTROL REGISTER I (SHARPNESS) 0x12 = 0x 11

[ 94.281634] tw9992_mipi CHROMA (U) GAIN REGISTER (SAT_U) 0x13 = 0x 80

[ 94.292702] tw9992_mipi CHROMA (V) GAIN REGISTER (SAT_V) 0x14 = 0x 80

[ 94.303365] tw9992_mipi HUE CONTROL REGISTER (HUE) 0x15 = 0x 0

[ 94.313970] tw9992_mipi VERTICAL PEAKING CONTROL I 0x17 = 0x 80

[ 94.325024] tw9992_mipi CORING CONTROL REGISTER (CORING) 0x18 = 0x 44

[ 94.335491] tw9992_mipi TEST MUX SELECTION 0x19 = 0x 6

[ 94.346214] tw9992_mipi CC/EDS STATUS REGISTER (CC_STATUS) 0x1A = 0x 10

[ 94.357322] tw9992_mipi CC/EDS DATA REGISTER (CC_DATA) 0x1B = 0x 0

[ 94.367950] tw9992_mipi STANDARD SELECTION (SDT) 0x1C = 0x f

[ 94.378468] tw9992_mipi STANDARD RECOGNITION (SDTR) 0x1D = 0x 7f

[ 94.389537] tw9992_mipi TEST 0x1F = 0x 0

[ 94.400040] tw9992_mipi CLAMPING GAIN (CLMPG) 0x20 = 0x 50

[ 94.410562] tw9992_mipi INDIVIDUAL AGC GAIN (IAGC) 0x21 = 0x 22

[ 94.421215] wm8960_mute set WM8960_CLOCK1

[ 94.421239] tw9992_mipi AGC GAIN (AGCGAIN) 0x22 = 0x f0

[ 94.425670] wm8960_mute set WM8960_CLOCK2

[ 94.435688] tw9992_mipi WHITE PEAK THRESHOLD (PEAKWT) 0x23 = 0x d8

[ 94.449913] tw9992_mipi CLAMP LEVEL (CLMPL) 0x24 = 0x bc

[ 94.461138] tw9992_mipi SYNC AMPLITUDE (SYNCT) 0x25 = 0x b8

[ 94.471794] tw9992_mipi SYNC MISS COUNT REGISTER (MISSCNT) 0x26 = 0x 44

[ 94.482524] tw9992_mipi CLAMP POSITION REGISTER (PCLAMP) 0x27 = 0x 38

[ 94.493917] tw9992_mipi VERTICAL CONTROL I 0x28 = 0x 0

[ 94.504669] tw9992_mipi VERTICAL CONTROL II 0x29 = 0x 0

[ 94.515382] tw9992_mipi COLOR KILLER LEVEL CONTROL 0x2A = 0x 78

[ 94.526197] tw9992_mipi COMB FILTER CONTROL 0x2B = 0x 44

[ 94.549012] tw9992_mipi LUMA DELAY AND HFILTER CONTROL 0x2C = 0x 30

[ 94.549371] wm8960_mute set WM8960_CLOCK1

[ 94.561561] tw9992_mipi MISCELLANEOUS CONTROL REGISTER I (MISC1) 0x2D = 0x 14

[ 94.563439] wm8960_mute set WM8960_CLOCK2

[ 94.573509] tw9992_mipi MISCELLANEOUS CONTROL REGISTER II (MISC2) 0x2E = 0x a5

[ 94.587493] tw9992_mipi MISCELLANEOUS CONTROL III (MISC3) 0x2F = 0x e0

[ 94.598802] tw9992_mipi MACROVISION DETECTION (MVSN) 0x30 = 0x 0

[ 94.610757] tw9992_mipi CHIP STATUS II (CSTATUS2) 0x31 = 0x 10

[ 94.621872] tw9992_mipi H MONITOR (HFREF) 0x32 = 0x ff

[ 94.628801] type=1400 audit(6177983978.156:6608): avc: denied { dac_read_search } for pid=5346 comm="main" capability=2 scontext=u:r:zygote:s0 tcontext=u:r:zygote:s0 tclass=capability permissive=0

[ 94.633506] tw9992_mipi CLAMP MODE (CLMD) 0x33 = 0x 5

[ 94.650072] type=1400 audit(6177983978.792:6616): avc: denied { dac_read_search } for pid=5383 comm="main" capability=2 scontext=u:r:zygote:s0 tcontext=u:r:zygote:s0 tclass=capability permissive=0

[ 94.660875] tw9992_mipi ID DETECTION CONTROL (NSEN/SSEN/PSEN/WKTH) 0x34 = 0x 1a

[ 94.688070] tw9992_mipi CLAMP CONTROL (CLCNTL) 0x35 = 0x 0

[ 94.698797] tw9992_mipi DIFFERENTIAL CLAMPING CONTROL 1 0x36 = 0x 5a

[ 94.710007] tw9992_mipi DIFFERENTIAL CLAMPING CONTROL 2 0x37 = 0x 18

[ 94.720383] wm8960_mute set WM8960_CLOCK1

[ 94.723046] tw9992_mipi DIFFERENTIAL CLAMPING CONTROL 3 0x38 = 0x dd

[ 94.724860] wm8960_mute set WM8960_CLOCK2

[ 94.734874] tw9992_mipi DIFFERENTIAL CLAMPING CONTROL 4 0x39 = 0x 0

[ 94.749260] tw9992_mipi SHORT DETECTION CONTROL 0x3A = 0x 30

[ 94.759725] tw9992_mipi SHORT DETECTION CONTROL 1 0x3B = 0x 0

[ 94.770121] tw9992_mipi DIFFERENTIAL CLAMPING CONTROL 5 0x3C = 0x 0

[ 94.781006] tw9992_mipi DIFFERENTIAL CLAMPING CONTROL 6 0x3D = 0x 0

[ 94.791503] tw9992_mipi LINENUMBER INT 0x3F = 0x 1a

[ 94.801963] tw9992_mipi WSS1 0x40 = 0x 80

[ 94.812857] tw9992_mipi WSS2 0x41 = 0x 0

[ 94.823292] tw9992_mipi WSS3 0x42 = 0x 0

[ 94.833701] tw9992_mipi IO BUFFER CONTROL 0x48 = 0x 2

[ 94.844658] tw9992_mipi DATA CONVERSION 0x49 = 0x 0

[ 94.855092] tw9992_mipi SYNC CONTROL 0x4A = 0x 81

[ 94.865558] tw9992_mipi OUTPUT CONTROL 0x4B = 0x a

[ 94.877057] tw9992_mipi POWER-DOWN REGISTER 0x4C = 0x 0

[ 94.887464] tw9992_mipi HSYNC OUTPUT ADJUSTMENT 0x4D = 0x 1

[ 94.897893] tw9992_mipi HSYNC OUTPUT ADJUSTMENT 0x4E = 0x 1

[ 94.908783] tw9992_mipi IRQ1 REGISTER 0x50 = 0x 0

[ 94.919207] tw9992_mipi IRQ2 REGISTER 0x51 = 0x 37

[ 94.929624] tw9992_mipi IRQ3 REGISTER 0x52 = 0x 0

[ 94.940554] tw9992_mipi INTERRUPT SOURCE STATUS 1 0x53 = 0x 0

[ 94.950969] tw9992_mipi INTERRUPT SOURCE STATUS 2 0x54 = 0x 6

[ 94.961386] tw9992_mipi INTERRUPT SOURCE STATUS 3 0x55 = 0x 0

[ 94.972415] tw9992_mipi IRQ1 ENABLE 0x56 = 0x 0

[ 94.982834] tw9992_mipi IRQ2 ENABLE 0x57 = 0x 0

[ 94.993738] tw9992_mipi IRQ3 ENABLE 0x58 = 0x 0

[ 95.004176] tw9992_mipi GPIO ENABLE 0x60 = 0x 0

[ 95.014613] tw9992_mipi GPIO OE 0x61 = 0x 0

[ 95.025510] tw9992_mipi GPIO OD 0x62 = 0x 0

[ 95.035949] tw9992_mipi GPIO ID 0x63 = 0x 0

[ 95.045933] tw9992_mipi

[ 95.048435] tw9992_mipi MIPI Transmitter Registers :

[ 95.054565] tw9992_mipi MIPI CONTROL, VIDEO INPUT FORMAT AND NUMBER OF DATA CHANNELS 0x70 = 0x 5

[ 95.065010] tw9992_mipi PICTURE WIDTH 0x71 = 0x a5

[ 95.075922] tw9992_mipi PICTURE WIDTH 0x72 = 0x a0

[ 95.086367] tw9992_mipi PICTURE HEIGHT 0x73 = 0x 0

[ 95.097299] tw9992_mipi PICTURE HEIGHT 0x74 = 0x f0

[ 95.109251] tw9992_mipi BLANK LINE NUMBER 0x75 = 0x 0

[ 95.120182] tw9992_mipi BLANK LINE NUMBER 0x76 = 0x 17

[ 95.130686] tw9992_mipi FRAME-START COUNT (FOR FS PACKET INSERTION) 0x77 = 0x 5

[ 95.142579] tw9992_mipi FRAME-START COUNT (FOR FS PACKET INSERTION) 0x78 = 0x 88

[ 95.153017] tw9992_mipi LINE START COUNT (FOR LS PACKET INSERTION) 0x79 = 0x 6

[ 95.163929] tw9992_mipi LINE START COUNT (FOR LS PACKET INSERTION) 0x7A = 0x 28

[ 95.175448] tw9992_mipi ACTIVE LINE START COUNT (FOR ACT-LS PACKET INSERTION) 0x7B = 0x 46

[ 95.186011] tw9992_mipi ACTIVE LINE START COUNT (FOR ACT-LS PACKET INSERTION) 0x7C = 0x b3

[ 95.196993] tw9992_mipi FRAME-END COUNT (FOR FE PACKET INSERTION) 0x7D = 0x 6

[ 95.207976] tw9992_mipi FRAME-END COUNT (FOR FE PACKET INSERTION) 0x7E = 0x 13

[ 95.218498] tw9992_mipi VIRTUAL CHANNEL NUMBERS 0x7F = 0x 10

[ 95.229447] tw9992_mipi WORD_COUNT IN LONG PACKET 0x80 = 0x 5

[ 95.240041] tw9992_mipi WORD_COUNT IN LONG PACKET 0x81 = 0x a0

[ 95.250523] tw9992_mipi D_PHY TIMING 0x82 = 0x 13

[ 95.261565] tw9992_mipi D-PHY TIMING 0x83 = 0x 11

[ 95.272969] tw9992_mipi D_PHY TIMING 0x84 = 0x 2

[ 95.285084] tw9992_mipi CLI-2 HS_CLK TIMING 0x85 = 0x e

[ 95.295756] tw9992_mipi D_PHY TIMING 0x86 = 0x 8

[ 95.306643] tw9992_mipi D_PHY TIMING 0x87 = 0x 37

[ 95.317829] tw9992_mipi MIPI D-PHY PARAMETERS 0x88 = 0x 0

[ 95.328552] tw9992_mipi SOT_PERIOD IN D-PHY 0x89 = 0x 0

[ 95.339395] tw9992_mipi EOT_PERIOD IN D-PHY 0x8A = 0x 2

[ 95.350510] tw9992_mipi D-PHY TIMING 0x8B = 0x 33

[ 95.361634] tw9992_mipi D-PHY TIMING 0x8C = 0x 22

[ 95.372148] tw9992_mipi D-PHY TIMING 0x8D = 0x 3

[ 95.382695] tw9992_mipi D-PHY TIMING 0x8E = 0x 22

[ 95.393354] wm8960_mute set WM8960_CLOCK1

[ 95.397874] wm8960_mute set WM8960_CLOCK2

[ 95.406329] tw9992_mipi D-PHY TIMING 0x8F = 0x 1

[ 95.417043] tw9992_mipi TEST PATTERN GENERATOR 0x90 = 0x 0

[ 95.428210] tw9992_mipi ESCAPE_MODE TIMING 0x91 = 0x c

[ 95.438838] tw9992_mipi AUTOMATIC TEST ERROR DETECTION 0x92 = 0x 0

[ 95.449963] tw9992_mipi FRAME-START LINE COUNT 0x93 = 0x e

[ 95.460499] tw9992_mipi PICTURE_HEIGHT HIGH BITS 0x94 = 0x 7

[ 95.471032] tw9992_mipi PICTURE_HEIGHT LOW BYTE 0x95 = 0x ff

[ 95.481645] tw9992_mipi SPECIAL HSCK COUNT 0x96 = 0x 1a

[ 95.492750] tw9992_mipi RESYNC-DELAY COUNT 0x9B = 0x 2

[ 95.503303] tw9992_mipi MIPI ANALOG CTRL DATA 0xA0 = 0x 0

[ 95.513830] tw9992_mipi MIPI ANALOG CTRL CLOCK 0xA1 = 0x 0

[ 95.524905] tw9992_mipi MIPI ANALOG CTRL MISC 0xA2 = 0x 30

[ 95.535473] tw9992_mipi MIPI ANALOG STATUS 0xA3 = 0x c0

[ 95.545820] wm8960_mute set WM8960_CLOCK1

[ 95.549043] tw9992_mipi MIPI ANALOG REGISTER 0xA4 = 0x 0

[ 95.550340] wm8960_mute set WM8960_CLOCK2

[ 95.559841] tw9992_mipi

[ 95.566441] tw9992_mipi ACA Registers :

[ 95.571236] tw9992_mipi ACA CONTROL 0xC0 = 0x 6

[ 95.581654] tw9992_mipi ACA GAIN CONTROL 0xC1 = 0x 20

[ 95.592721] tw9992_mipi Y AVERAGE HIGH LIMIT CONTROL 0xC2 = 0x 30

[ 95.603177] tw9992_mipi Y AVERAGE LOW LIMIT CONTROL 0xC3 = 0x 0

[ 95.613582] tw9992_mipi Y DETECTION THRESHOLD 0xC4 = 0x 9

[ 95.624644] tw9992_mipi BLACK LEVEL 0xC5 = 0x 10

[ 95.635048] tw9992_mipi CENTER LEVEL 0xC6 = 0x 6

[ 95.645728] tw9992_mipi WHITE LEVEL 0xC7 = 0x 0

[ 95.656772] tw9992_mipi MEAN OFFSET LIMIT 0xC8 = 0x 58

[ 95.668228] tw9992_mipi MEAN OFFSET SLOPE 0xC9 = 0x 10

[ 95.679301] tw9992_mipi MEAN OFFSET UP GAIN 0xCA = 0x 1e

[ 95.690361] tw9992_mipi MEAN OFFSET DOWN GAIN 0xCB = 0x 1a

[ 95.701890] tw9992_mipi DELTA CUTOFF THRESHOLD 0xCC = 0x a

[ 95.713322] tw9992_mipi DELTA SLOPE 0xCD = 0x 1f

[ 95.725418] tw9992_mipi LOW/HIGH AVERAGE THRESHOLD 0xCE = 0x 1a

[ 95.736629] tw9992_mipi LOW MAX LEVEL CONTROL 0xCF = 0x e

[ 95.747526] tw9992_mipi HIGH MAX LEVEL CONTROL 0xD0 = 0x e

[ 95.758066] tw9992_mipi LOW UP GAIN CONTROL 0xD1 = 0x e

[ 95.768978] tw9992_mipi LOW DOWN GAIN CONTROL 0xD2 = 0x c

[ 95.779631] tw9992_mipi HIGH UP GAIN CONTROL 0xD3 = 0x a

[ 95.789704] wm8960_mute set WM8960_CLOCK1

[ 95.794175] wm8960_mute set WM8960_CLOCK2

[ 95.802461] tw9992_mipi HIGH DOWN GAIN CONTROL 0xD4 = 0x e

[ 95.813042] tw9992_mipi LOW PASS FILTER COEFFICIENT 0xD5 = 0x 4

[ 95.824149] tw9992_mipi PDF INDEX 0xD6 = 0x 0

[ 95.834644] tw9992_mipi HISTOGRAM WINDOW H START 0xD7 = 0x 0

[ 95.837393] wm8960_mute set WM8960_CLOCK1

[ 95.845545] tw9992_mipi HISTOGRAM WINDOW H SIZE 0xD8 = 0x 1

[ 95.849016] wm8960_mute set WM8960_CLOCK2

[ 95.860004] tw9992_mipi HISTOGRAM WINDOW H SIZE 0xD9 = 0x 68

[ 95.873192] tw9992_mipi HISTOGRAM WINDOW V START 0xDA = 0x 0

[ 95.884235] tw9992_mipi HISTOGRAM WINDOW V SIZE 0xDB = 0x 1

[ 95.894638] tw9992_mipi HISTOGRAM WINDOW V SIZE 0xDC = 0x 20

[ 95.905515] tw9992_mipi Y AVERAGE 0xE0 = 0x 35

[ 95.916028] tw9992_mipi Y AVERAGE LIMIT 0xE1 = 0x 40

[ 95.926564] tw9992_mipi LOW AVERAGE 0xE2 = 0x 30

[ 95.937725] tw9992_mipi HIGH AVERAGE 0xE3 = 0x 58

[ 95.948121] tw9992_mipi Y MAX 0xE4 = 0x 1c

[ 95.958792] tw9992_mipi Y MIN 0xE5 = 0x 52

[ 95.969266] tw9992_mipi MOFFSET 0xE6 = 0x 39

[ 95.979878] tw9992_mipi LOW GAIN 0xE7 = 0x c3

[ 95.990857] tw9992_mipi HIGH GAIN 0xE8 = 0x 25

[ 96.001390] tw9992_mipi LL SLOPE 0xE9 = 0x 48

[ 96.011972] tw9992_mipi LH SLOPE 0xEA = 0x d0

[ 96.022727] tw9992_mipi HL SLOPE 0xEB = 0x 36

[ 96.033160] tw9992_mipi HH SLOPE 0xEC = 0x 1e

[ 96.043706] tw9992_mipi X LOW 0xED = 0x 28

[ 96.054155] tw9992_mipi X MEAN 0xEE = 0x 40

[ 96.064549] tw9992_mipi X HIGH 0xEF = 0x 95

[ 96.074992] tw9992_mipi Y LOW 0xF0 = 0x 2b

[ 96.085421] tw9992_mipi Y MEAN 0xF1 = 0x 79

[ 96.096295] tw9992_mipi Y HIGH 0xF2 = 0x c2

[ 96.106731] tw9992_mipi ACA CONTROL 0xF3 = 0x 2

[ 96.117579] tw9992_mipi ACA CONTROL 0xF4 = 0x 0

[ 96.128008] tw9992_mipi ACA CONTROL 0xF5 = 0x 0

[ 96.138275] ---> tw9992_get_fmt

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Report Inappropriate Content

Note: for blending mode, two ISI channels are used, and ISI0 is must, it is the final output to memory channel, another channel can be ISI1~7.

Register dump:

[ 26.295609] bypass csc

[ 26.300163] input fmt YUV4

[ 26.308487] output fmt YUYV

[ 26.624426] mxc-isi 58100000.isi: ISI CHNLC register dump, isi0

[ 26.630393] mxc-isi 58100000.isi: CHNL_CTRL 0x0h = 0xc0000015

[ 26.637664] mxc-isi 58100000.isi: CHNL_IMG_CTRL 0x4h = 0x20000009

[ 26.644706] mxc-isi 58100000.isi: CHNL_OUT_BUF_CTRL 0x8h = 0x c000

[ 26.651705] mxc-isi 58100000.isi: CHNL_IMG_CFG 0xCh = 0x 1e002d0

[ 26.658739] mxc-isi 58100000.isi: CHNL_IER 0x10h = 0x3dfb0000

[ 26.665746] mxc-isi 58100000.isi: CHNL_STS 0x14h = 0x 100

[ 26.672776] mxc-isi 58100000.isi: CHNL_SCALE_FACTOR 0x18h = 0x10001000

[ 26.679773] mxc-isi 58100000.isi: CHNL_SCALE_OFFSET 0x1Ch = 0x 8000000

[ 26.686804] mxc-isi 58100000.isi: CHNL_CROP_ULC 0x20h = 0x 0

[ 26.693819] mxc-isi 58100000.isi: CHNL_CROP_LRC 0x24h = 0x 0

[ 26.700847] mxc-isi 58100000.isi: CHNL_CSC_COEFF0 0x28h = 0x 0

[ 26.707843] mxc-isi 58100000.isi: CHNL_CSC_COEFF1 0x2Ch = 0x 0

[ 26.714870] mxc-isi 58100000.isi: CHNL_CSC_COEFF2 0x30h = 0x 0

[ 26.721877] mxc-isi 58100000.isi: CHNL_CSC_COEFF3 0x34h = 0x 0

[ 26.728908] mxc-isi 58100000.isi: CHNL_CSC_COEFF4 0x38h = 0x 0

[ 26.735912] mxc-isi 58100000.isi: CHNL_CSC_COEFF5 0x3Ch = 0x 0

[ 26.742938] mxc-isi 58100000.isi: CHNL_ROI_0_ALPHA 0x40h = 0x 0

[ 26.749944] mxc-isi 58100000.isi: CHNL_ROI_0_ULC 0x44h = 0x 0

[ 26.756973] mxc-isi 58100000.isi: CHNL_ROI_0_LRC 0x48h = 0x 0

[ 26.763983] mxc-isi 58100000.isi: CHNL_ROI_1_ALPHA 0x4Ch = 0x 0

[ 26.771007] mxc-isi 58100000.isi: CHNL_ROI_1_ULC 0x50h = 0x 0

[ 26.778011] mxc-isi 58100000.isi: CHNL_ROI_1_LRC 0x54h = 0x 0

[ 26.785035] mxc-isi 58100000.isi: CHNL_ROI_2_ALPHA 0x58h = 0x 0

[ 26.792049] mxc-isi 58100000.isi: CHNL_ROI_2_ULC 0x5Ch = 0x 0

[ 26.799073] mxc-isi 58100000.isi: CHNL_ROI_2_LRC 0x60h = 0x 0

[ 26.806084] mxc-isi 58100000.isi: CHNL_ROI_3_ALPHA 0x64h = 0x 0

[ 26.813114] mxc-isi 58100000.isi: CHNL_ROI_3_ULC 0x68h = 0x 0

[ 26.820123] mxc-isi 58100000.isi: CHNL_ROI_3_LRC 0x6Ch = 0x 0

[ 26.827152] mxc-isi 58100000.isi: CHNL_OUT_BUF1_ADDR_Y 0x70h = 0xa6b00000

[ 26.834150] mxc-isi 58100000.isi: CHNL_OUT_BUF1_ADDR_U 0x74h = 0x 0

[ 26.841185] mxc-isi 58100000.isi: CHNL_OUT_BUF1_ADDR_V 0x78h = 0x 0

[ 26.848177] mxc-isi 58100000.isi: CHNL_OUT_BUF_PITCH 0x7Ch = 0x 5a0

[ 26.855199] mxc-isi 58100000.isi: CHNL_IN_BUF_ADDR 0x80h = 0xa6900000

[ 26.862206] mxc-isi 58100000.isi: CHNL_IN_BUF_PITCH 0x84h = 0x 5a0

[ 26.869236] mxc-isi 58100000.isi: CHNL_MEM_RD_CTRL 0x88h = 0xd0000000

[ 26.876232] mxc-isi 58100000.isi: CHNL_OUT_BUF2_ADDR_Y 0x8Ch = 0xa6600000

[ 26.883254] mxc-isi 58100000.isi: CHNL_OUT_BUF2_ADDR_U 0x90h = 0x 0

[ 26.890254] mxc-isi 58100000.isi: CHNL_OUT_BUF2_ADDR_V 0x94h = 0x 0

[ 26.897259] mxc-isi 58100000.isi: CHNL_SCL_IMG_CFG 0x98h = 0x 1e002d0

[ 26.904282] mxc-isi 58110000.isi: ISI CHNLC register dump, isi1

[ 26.910243] mxc-isi 58110000.isi: CHNL_CTRL 0x0h = 0xc0000002

[ 26.917263] mxc-isi 58110000.isi: CHNL_IMG_CTRL 0x4h = 0x20004001