- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Where is the OCRAM (FlexRAM) in the i.MX Rt 1060?

Where is the OCRAM (FlexRAM) in the i.MX Rt 1060?

Where is the OCRAM (FlexRAM) in the i.MX Rt 1060?

Hi All

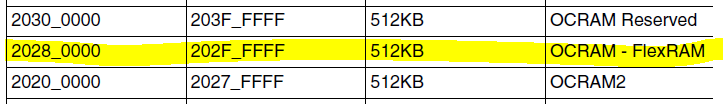

According to the user's manual for the i.MX RT 1060 the OCRAM (FlexRAM) occupies the address range from 0x20280000:

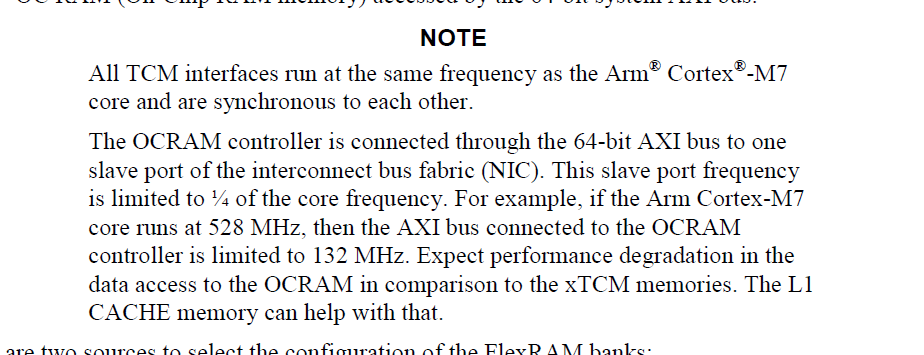

The FlexRAM default is to have 128k DTC, 128k ITC and 256k OCRAM and its OCRAM2 is fixed at 0x20200000 (512k).

When I try to use OCRAM I find that there are access errors on all addresses in the OCRAM (FlexRAM) range, although ITC and DTC accesses are OK (in their 128k default ranges), as are accesses in OCRAM2 area.

If I then reconfigure the FlexRAM I can configure both ITC and DTC to have sizes of 32k..512k, as expected but no matter what size is allocated to the OCRAM it can never be accessed. If I allocate all of FlexRAM to the OCRAM there is neither ITC nor DTC (correct) but there is still no OCRAM in the area.

Questions:

- is the OCRAM accessible in a different address range than reported in the user's manual?

- is there some additional control needed to allow the OCRAM to operate? (its clock is enabled by default and I haven't located further methods to enable/disable it)

- could it be an issue with my EVKB? (eg. a missing power line needed for this memory)?

Thanks

Regards

Mark

[uTasker project developer for Kinetis and i.MX RT]

Hi Mark Butcher ,

Do you have read the following flexRAM application note?

https://www.nxp.com/docs/en/application-note/AN12077.pdf

You will find more details about the flexRAM, OCRAM, ITCM and DTCM.

- is the OCRAM accessible in a different address range than reported in the user's manual?

Answer: No, the RT1060 OCRAM address is just defined in the reference manual.

- is there some additional control needed to allow the OCRAM to operate? (its clock is enabled by default and I haven't located further methods to enable/disable it)

Answer: About the OCRAM clock, please check the application note which I give you.

- could it be an issue with my EVKB? (eg. a missing power line needed for this memory)?

Answer: As I know, it is not the EVKB problems.

You can double check the application note, and check whether you meet the application note requirement.

Best Regards,

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Kerry

I have been following the application note, which matches for the i.MX RT 1010, i.MX RT 1020 and i.MX RT 1050. It however doesn't match for the i.MX RT 1060 or i.MX RT 1064.

According to the default for both RT105x and RT106x there should be 256k of OCRAM available after reset (when the eFuses are left in the default state):

If one connects to the board with a debugger one can read and write in the areas 0x00000000..0x0001ffff [128k ITC] and 0x20000000..0x2001ffff [128k DTC], and also in the area 0x20200000..0x2027ffff [512k OCRAM2 fixed], but one can't access the area 0x20280000...0x202b0000, which should be the default 256k OCRAM FlexRAM.

This is a very simple test to do (doesn't even need code). Do you manage to use/access the OCRAM or access any memory in the area 0x20280000...0x202fffff?

I can then reprogram the FlexRAM to allocate different sizes of ITC and DTC and OCRAM [all according to the application note, which does work on the i.MX RT 105x] and it works normally for the ITC and DTC but there is never OCRAM available.....

I another post I pointed out that the i.MX RT 1015 has 256k of FlexRAM, rather than the 128k as indicated in its data sheet.

How much SRAM does the i.MX RT 1015 have?

and it also behaves in exactly the same ways as an RT1020 with respect to FlexRAM in the application note, therefore I presently am not sure what to believe from the documentation.

Regards

Mark

HI Mark Butcher,

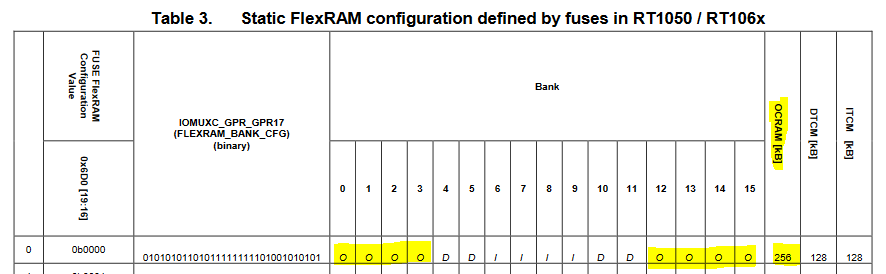

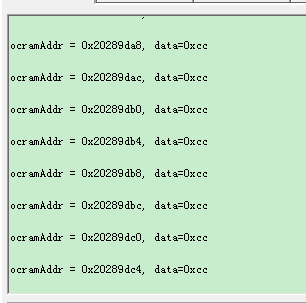

Do you test the RT1060 SDK flexRAM project? That project can write and read the related OCRAM flexRAM area, this is my test result:

You can find the the related flexRAM OCRAM can be write and read.

Could you please test that project again?

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

Hi Kerry

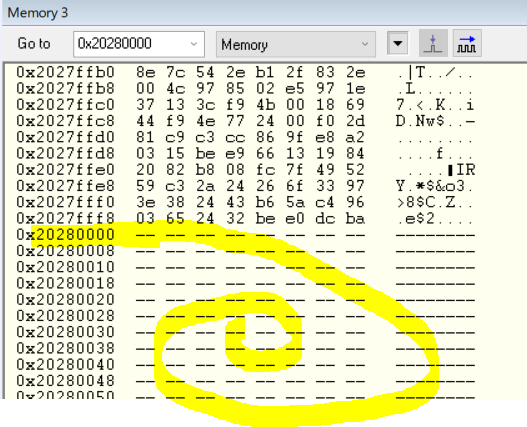

If you open a memory view in IAR do you see it at that point where you stopped?

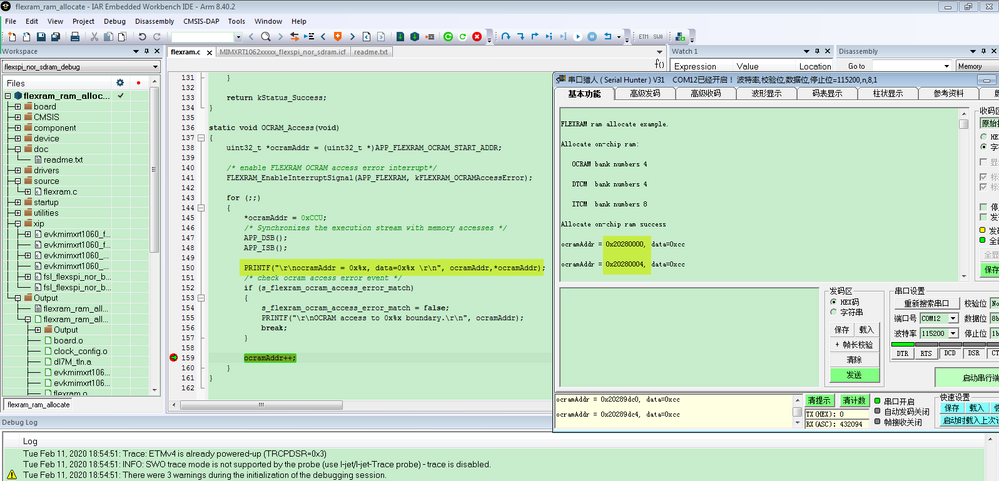

It seems that this is an IAR problem since when I try to view the OCRAM (FlexRAM) memory it shows this:

0x2027fff8 is the last line in OCRAM2.

And after that it display just dashes, as it does when it can't access memory.

However when I add a read/write test to the code itself it works.

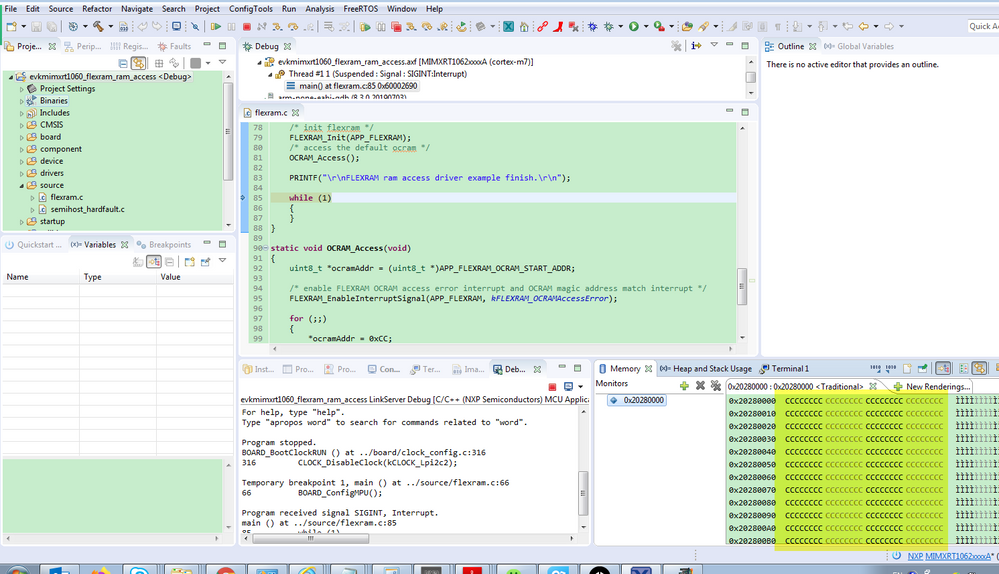

Also, when I do the same in MCUXpresso's memory viewer I "can" see the memory.

Before I had always trusted IAR's viewer but - especially if you can confirm - it must mean that they have set something up incorrectly to automatically block accesses in the OCRAM area. Potentially it also explains another problem I had with the i.MX RT 1015 where I couldn't view memory after a certain address!

Regards

Mark

Hi Mark Butcher,

The same viewpoint with you, I also find the IAR memory problems yesterday, that's why I printf all the data out and show to you, I think it is the IAR bugs.

But the MCUXpresso IDE can show the related address:

So, normally, when I meet the IDE can't show the memory data, I will use the printf to test it again, just make sure it is not related to the IDE. About the RT1015, I think you can test it the same way instead of just use the IDE memory window to check it.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if yo

Kerry

Yes, I agree that this is an IAR bug.

Today I completed work on the i.MX RT 1060 whereby I boot up with the stack pointer at the top of OCRAM and then switch to it at the top of DTC after re-configuring the FlexRAM to allocate 480k TDC and 32k ITC (when the program code is less that 32k, or dynamically to suit the best mix between code and data).

It was not possible to watch the details in IAR (due to its viewing problem) but the operation was successful, showing that all FlexRAM is there and does work as it should.

Also I have a memory debugger in the application allowing me to view and modify memory addresses, where I can confirm such things when the memory view causes doubts.

Regards

Mark

P.S. Did you look at the i.MX RT 1015 thread? https://community.nxp.com/thread/523554

I added a video showing that I can use 256k RAM on a 128k part - do you have an explanation???

Hi Mark Butcher,

Thanks for your confirmation, and that's very good to hear it really works on your side with MIMXRT1060.

About your MIMXRT1015 thread, my colleague Victor Jimenez already take it and reply it.

You can @ him again to give you reply!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------