- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Audio sai2 mclk

Audio sai2 mclk

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Audio sai2 mclk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I am using imx6ul, the kernel is linux4.14.78,

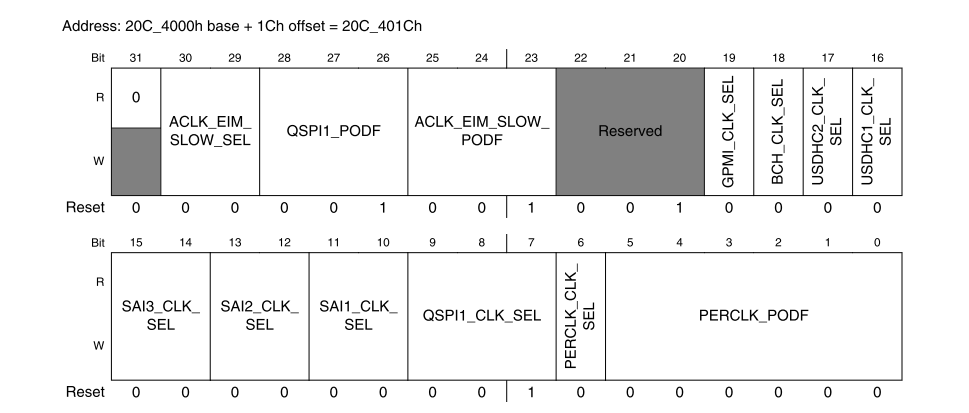

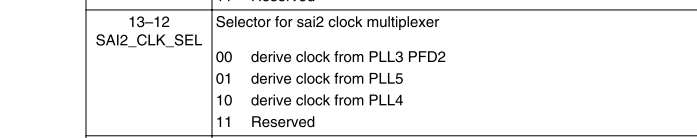

I used the i2s external audio chip, but the audio clock is wrong and I can't generate the clock I want. I checked the imx6ul chip manual and found

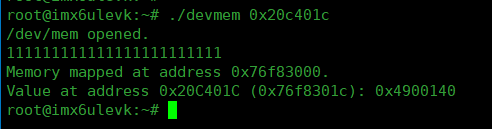

The register configuration is 10 for PLL4 as the parent clock. But I read it out is 00.

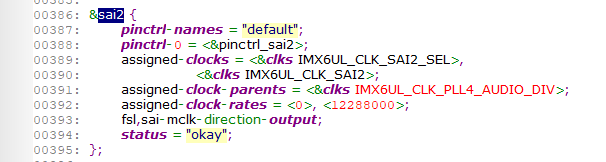

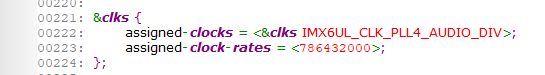

My device tree configures the PLL4 bit parent clock

I should do it exclusively?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Jiehuai,

From source code below, we can know the clock outputs on JTAG_TMS PAD:

pinctrl_sai2: sai2grp {

fsl,pins = <

MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x17088

MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x17088

MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x11088

MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x11088

MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x17088

MX6UL_PAD_SNVS_TAMPER4__GPIO5_IO04 0x17059

>;

};

after system booting is done, you can play a music file, then measure the clock on the JTAG_TMS Pin to check if the clock value is what you want.

(系统启动后,播放一个音乐文件,然后用示波器在这个脚上测一下clock的值是否是你希望的12.288MHz, PLL4配置为786432000Hz,它是12288000Hz的整数倍,配置上是对的,输出的clock应该是正确的。所以,请示波器测量一下,看实际结果)

Have a nice day!

BR,

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

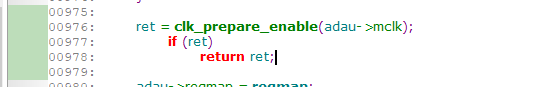

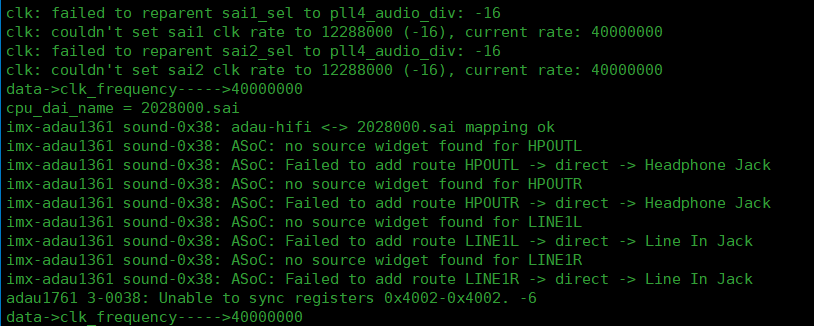

thank you for your reply

After I enable the frequency, I start the error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiehuai,

On i.MX6UL EVK, default I2S port is also SAI2, so you don't need to change source code if you also use the same codec as that of EVK, below is source code in dts:

pinctrl_i2c2: i2c2grp {

fsl,pins = <

MX6UL_PAD_UART5_TX_DATA__I2C2_SCL 0x4001b8b0

MX6UL_PAD_UART5_RX_DATA__I2C2_SDA 0x4001b8b0

>;

};

......

/* Here is sound card , Machine driver will be loaded here */

sound: sound {

compatible = "fsl,imx6ul-evk-wm8960",

"fsl,imx-audio-wm8960";

model = "wm8960-audio";

cpu-dai = <&sai2>;

audio-codec = <&codec>;

asrc-controller = <&asrc>;

codec-master;

gpr = <&gpr 4 0x100000 0x100000>; /* This is SAI2_MCLK setting in GPR register */

/*

* hp-det = <hp-det-pin hp-det-polarity>;

* hp-det-pin: JD1 JD2 or JD3

* hp-det-polarity = 0: hp detect high for headphone

* hp-det-polarity = 1: hp detect high for speaker

*/

hp-det = <3 0>;

hp-det-gpios = <&gpio5 4 0>;

mic-det-gpios = <&gpio5 4 0>;

audio-routing =

"Headphone Jack", "HP_L",

"Headphone Jack", "HP_R",

"Ext Spk", "SPK_LP",

"Ext Spk", "SPK_LN",

"Ext Spk", "SPK_RP",

"Ext Spk", "SPK_RN",

"LINPUT2", "Mic Jack",

"LINPUT3", "Mic Jack",

"RINPUT1", "Main MIC",

"RINPUT2", "Main MIC",

"Mic Jack", "MICB",

"Main MIC", "MICB",

"CPU-Playback", "ASRC-Playback",

"Playback", "CPU-Playback",

"ASRC-Capture", "CPU-Capture",

"CPU-Capture", "Capture";

};

........

&clks {

assigned-clocks = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <786432000>;

};

......

&i2c2 {

clock_frequency = <100000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_i2c2>;

status = "okay";

codec: wm8960@1a {

#sound-dai-cells = <0>;

compatible = "wlf,wm8960";

reg = <0x1a>;

wlf,shared-lrclk;

clocks = <&clks IMX6UL_CLK_SAI2>;

clock-names = "mclk";

};

......

pinctrl_sai2: sai2grp {

fsl,pins = <

MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x17088

MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x17088

MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x11088

MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x11088

MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x17088

MX6UL_PAD_SNVS_TAMPER4__GPIO5_IO04 0x17059

>;

};

......

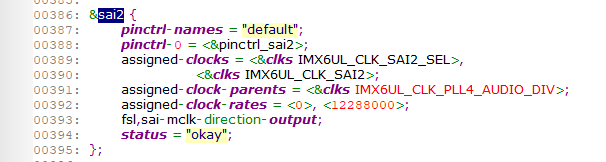

&sai2 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sai2>;

assigned-clocks = <&clks IMX6UL_CLK_SAI2_SEL>,

<&clks IMX6UL_CLK_SAI2>;

assigned-clock-parents = <&clks IMX6UL_CLK_PLL4_AUDIO_DIV>;

assigned-clock-rates = <0>, <12288000>;

fsl,sai-mclk-direction-output;

status = "okay";

};

Are you using i.MX6UL EVK to test it?

BR,

Weidong

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thank you for your reply

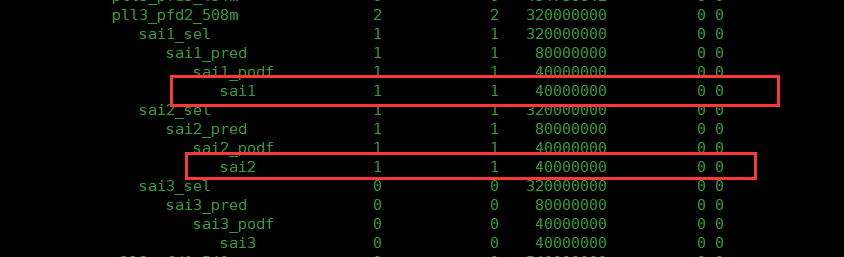

I look at the clock tree

according to dts

sai2 Parent clock is IMX6UL_CLK_PLL4_AUDIO_DIV

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Are you using i.MX6UL EVK to test it?

weidong