- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- Memory resources used for boot loader for LPC54606

Memory resources used for boot loader for LPC54606

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

Memory resources used for boot loader for LPC54606

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I also have a separate but related question around the internal flash programming. Is the only way to program/erase the internal flash, from the user application code or the IAR flash writer’s monitor code, by calling the IAP (boot rom) flash programming APIs? If so, can you please clarify on the amount of SRAM0 these boot ROM/IAP can use? 41.3.8.2 is troubling. If the internal boot rom/IAP calls require access to the SRAM0 (or other memory/shared resources) then Microsoft needs to have a list of all such usages, for their secondary boot loader. If their application needs to call the IAP APIs then they would need to budget resources accordingly. Thank you.

I noticed I had not identified the technology sector. Sorry for the dual entry of the same thing.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you.

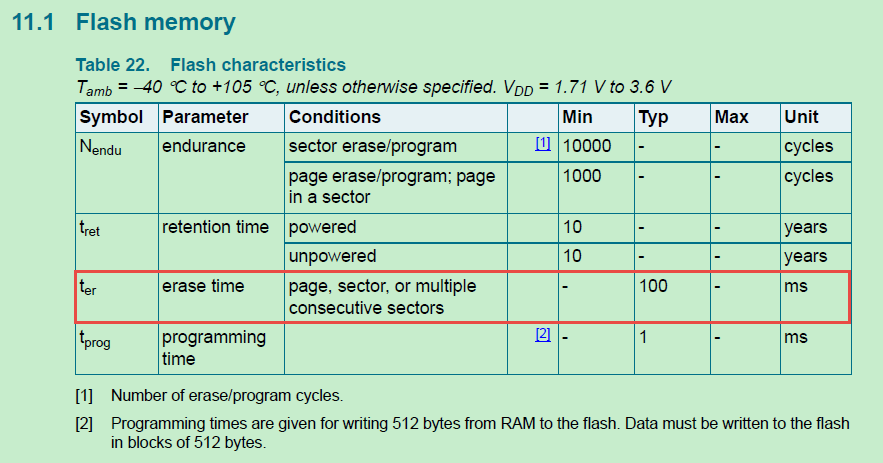

I have been unsuccessful in locating this information in the datasheet. Can you Provide some numbers for the follow? MS needs typical and worst case numbers for each item.

Flash erase latency for page erase (256 bytes)

Flash erase latency for sector erase (32K bytes)

Flash program latency for 256 byte page

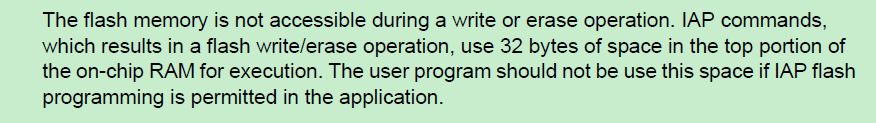

My understanding is that the MCU is unable to XIP from flash during a flash erase/program operation, is this correct? Is there a way to suspend an active flash erase/program operation to allow XIP to continue, and to resume the flash operation at a later time?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Chapter 11.1 Flash memory shows the typical time for Flash erase time is 100ms.

The flash memory is not accessible during a write or erase operation.

So, LPC5460x is unable to XIP from flash during a falsh erase/program operation.

There is an application note AN11333 about Interrupt handling during IAP calls for LPC product.

More detailed info, please check below link:

https://www.lpcware.com/content/nxpfile/an11333-interrupt-handling-during-iap-calls-lpc177x8x-and-lp...

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

This is on the OM13092 board with the on board debugger and the IAR tool chain.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

About IAR IDE reserve RAM range for IAP flash programming, customer could redefine the RAM memory size(remove 128 byte from RAM size) at IAR link configure file (ICF file).

Wish it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Why should you reserve 128 bytes at the end of the memory for this ??

It says in the UM, 41.3.8.3 that the space used by the IAP routines are used from the users stackspace (so no reason to "reserve" anything in the memory map (for the linker), just make sure the user stack is large enough to encompass the 128 bytes needed of stack space by the IAP functions:

41.3.8.3 RAM used by IAP command handler

Flash programming commands use the user stack space and may use up to 128 bytes

growing downward.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Carsten,

You are right. The user manual chapter 41.3.8.3 shows the user stack space usage is up to 128bytes.

While in user manual page 1029 with below description:

So, the top portion of SRAM need reserved 32 byte for IAP application, not 128 bytes.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Yes, it need to call the ROM Flash API to do LPC54608 Flash operation.

Customer call the the ROM Flash API from secondary bootloader is IAP command handler.

From the chapter 41.3.8.3, the Flash programming commands use the user stack space and may use up to 128 bytes.

So, please refer below link to reserve RAM for IAP flash programming:

Reserving RAM for IAP Flash Programming | www.LPCware.com

And customer also could refer below thread for more detailed info about secondary bootloader application:

IAP RAM Requirements? | www.LPCware.com

Wis it helps.

Have a great day,

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------