- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Failed to execute /init (error -8) during android bringup

Failed to execute /init (error -8) during android bringup

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We have designed a custom board based on SabreSD. We are trying to bring Android Kitkat (4.4.3)up on the platform. We have downloaded the android source tree, applied patches available on freescale website and have generated the necessary images. When we try to boot the board from SD card, we get the following error.

Failed to execute /init

Failed to execute /init. Attempting defaults...

Kernel panic - not syncing: No init found. Try passing init= option to kernel. See Linux Documentation/init.txt for guidance.

After adding some patches to main.c file we found the kernel returned error code 8 (ENOEXEC) when trying to execute it. The built images boot well on SabreSD. The major difference between the SabreSD board and our custom board is that our custom board has 1GB LPDDR2 RAM instead of DDR3 found on SabreSD. Any help on debugging this issue is greatly appreciated.

Thanks

Vijai

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I solved my problem, perhaps it helps you also. Visit my thread:

Re: Problems configuring 2-Channel LPDDR2 on i.MX6Q

Greetings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

we are also using the same LPDDR2 part number. I am facing DDR memory test failure issue.

Could you share the MMDC configuration scripts as you used.

Regards,

Selvakumar V

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vijai,

Have you ensured that your build configurations are considering the proper initializations for LPDDR2 instead of DDR3?

Hope this will be useful for you.

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Carlos,

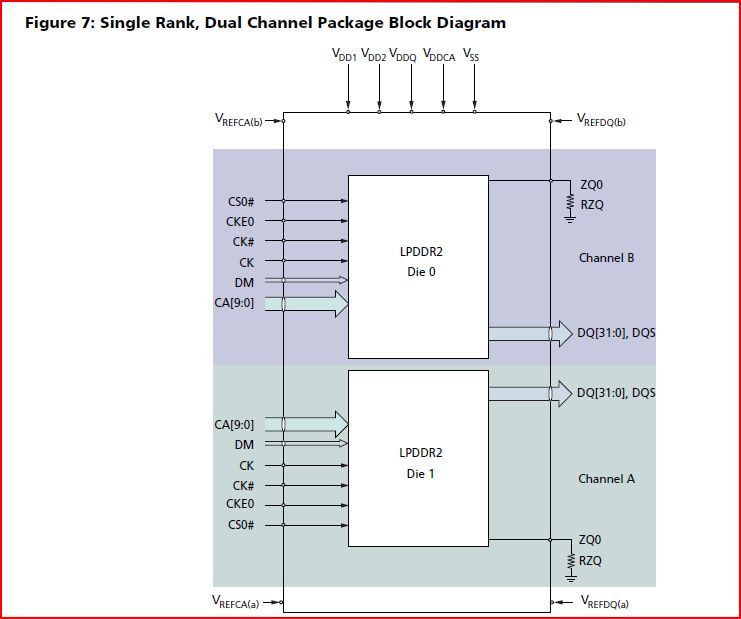

Thank you for replying. I have a doubt in the DDR settings. One of our team have ported 3.18 kernel on our custom board. We have added some patches in uboot to detect both the banks. We use MT42L128M64D2 LPDDR2 RAM. Even though 1G of RAM is detected in uboot and Kernel(3.18.7), we were unable to do a memory test. The issue we are facing is similar to the one posted here

Problems configuring 2-Channel LPDDR2 on i.MX6Q

Could you kindly have a look at it and advise us on the same. I would love to move this discussion to the above location.

We use Mx6DQSDL LPDDR2 Script Aid V0.04.xlsx to generate values for our DCD table.

Our system configuration is as follows

Kernel: 3.18.7

Uboot: 2014.10

Note:

For Android we are using Freescale supplied 3.10.53 android kernel and 2014.04 uboot.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I solved my problem, perhaps it helps you also. Visit my thread:

Re: Problems configuring 2-Channel LPDDR2 on i.MX6Q

Greetings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi vijaikumar

The init process is decided by cmdline. You can change lp5.1_evk_6sl_4_24/device/fsl/sabresd_6dq/BoardConfig.mk

The mark line decide where is the init executable file.

BOARD_KERNEL_CMDLINE := console=ttymxc0,115200 init=/init video=mxcfb0:dev=ldb,bpp=32 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off vmalloc=400M androidboot.console=ttymxc0 consoleblank=0 androidboot.hardware=freescale cma=384M

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sanshanzhang ,

I see that the init=/init is mentioned in the boot arguments and is pointing to the correct location. Following is the boot arguments used by me.

setenv bootargs console=ttymxc0,115200 init=/init video=mxcfb0:dev=hdmi,1920x1080M@60 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=10M vmalloc=100M androidboot.console=ttymxc0 consoleblank=0 androidboot.hardware=freescale cma=384M

Our board boots successfully (no init error) when I give the following boot arguments. i.e. changed the memory to 512MB instead of 1GB.

setenv bootargs console=ttymxc0,115200 init=/init video=mxcfb0:dev=hdmi,1920x1080M@60 video=mxcfb1:off video=mxcfb2:off video=mxcfb3:off fbmem=10M vmalloc=100M androidboot.console=ttymxc0 consoleblank=0 androidboot.hardware=freescale cma=200M mem=512M

I am suspecting the DRAM initialization, eventhough it shows 1GB of memory I doubt that it actually uses it. As mentioned in previous comment, we are using Freescale's LPDDR2 script aid to generate values for our DCD table. (Kindly refer my response to CarlosCasillas above )

I hope someone from Freescale will help us resolve our issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Vijai,

Taking apart the software, have you calibrated your DDR memory specifically on your board?

You could take a look at application note AN4467 "i.MX 6 Series DDR Calibration" at the following link:

http://www.freescale.com/files/32bit/doc/app_note/AN4467.pdf

Hope this will be useful for you.

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CarlosCasillas ,

I used the DDR stress test tool available from Freescale to do a read and write calibration. I see that by reading BOOT_CFG3[5-4], the tool detects it as a single channel. Attached the log for the same. Can you kindly let me know if any changes are required in the BOOT_CFG[5:4] for DDR part MT42L128M64D2. Will the BOOT_CFG3 produce issues when configured incorrectly for Single channel?

Following is the block diagram of the DDR.