- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: lpspi reading jedecID from flash

lpspi reading jedecID from flash

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello

on the 105x

trying to use lpspi interface to initiate spi transactions

I am using the SDK example: lpspi_btb_interrupt_master

I am connected to an external board with the flash

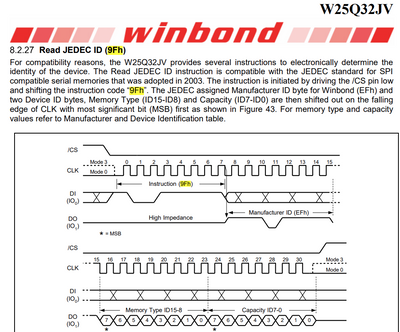

trying to read the JEDEC ID with opcode 0x9F according to windbond spec:

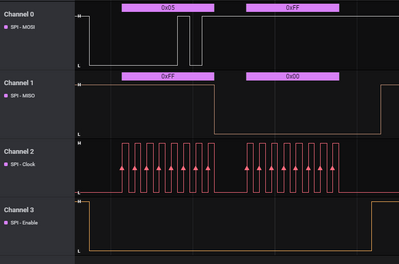

but I dont receive any data on the MISO line:

or with the lpspi poliing example:

when using the FLEX_SPI interface, with SDK example "nor_polling_transfer" ,no problems:

what could be the issue?

maybe these examples lpspi_btb_interrupt_master and lpspi_btb_polling_master are not fit to this kind of task? maybe they are BTB dedicated?

thanks

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the issue was some hardware issues

example reading jedec code:

/*Master config*/

LPSPI_MasterGetDefaultConfig(&masterConfig);

masterConfig.baudRate = TRANSFER_BAUDRATE;

masterConfig.whichPcs = EXAMPLE_LPSPI_MASTER_PCS_FOR_INIT;

srcClock_Hz = LPSPI_MASTER_CLK_FREQ;

LPSPI_MasterInit(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterConfig, srcClock_Hz);

uint32_t jedecId;

uint8_t readdata;

PRINTF("READ JEDEC");

jedecId = 0;

masterTxData[0] = 0x9F;

masterTxData[1] = 0xFF;

masterTxData[2] = 0xFF;

masterTxData[3] = 0xFF;

masterTxData[4] = 0xFF;

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = masterTxData;

masterXfer.rxData = &jedecId;

masterXfer.dataSize = 4;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

example for reading and programming page in 4 byte mode (32 bit address, after sending 0xB7 opcode):

PRINTF("READ ADDRESS 0X0");

uint8_t page[262];

masterTxData[0] = 0x0B;

masterTxData[1] = 0x0;

masterTxData[2] = 0x0;

masterTxData[3] = 0x0;

masterTxData[4] = 0x0;

masterTxData[5] = 0xFF; //DUMMY BYTE

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = masterTxData;

masterXfer.rxData = page;

masterXfer.dataSize = 262;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_SetDummyData(EXAMPLE_LPSPI_MASTER_BASEADDR, 0xFF); // Set dummy data to 0xFF

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

PRINTF("WR EN");

masterTxData[0] = 0x06;

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = masterTxData;

masterXfer.rxData = NULL;

masterXfer.dataSize = 1;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

PRINTF("PROGRAM ADDRESS 0X0");

uint8_t progpage[267];

int i;

for( i=5;i<267;i++)

{

progpage[i] = i - 5;

}

progpage[0] = 0x02;

progpage[1] = 0x0;

progpage[2] = 0x0;

progpage[3] = 0x0;

progpage[4] = 0x0;

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = progpage;

masterXfer.rxData = NULL;

masterXfer.dataSize = 262;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the issue was some hardware issues

example reading jedec code:

/*Master config*/

LPSPI_MasterGetDefaultConfig(&masterConfig);

masterConfig.baudRate = TRANSFER_BAUDRATE;

masterConfig.whichPcs = EXAMPLE_LPSPI_MASTER_PCS_FOR_INIT;

srcClock_Hz = LPSPI_MASTER_CLK_FREQ;

LPSPI_MasterInit(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterConfig, srcClock_Hz);

uint32_t jedecId;

uint8_t readdata;

PRINTF("READ JEDEC");

jedecId = 0;

masterTxData[0] = 0x9F;

masterTxData[1] = 0xFF;

masterTxData[2] = 0xFF;

masterTxData[3] = 0xFF;

masterTxData[4] = 0xFF;

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = masterTxData;

masterXfer.rxData = &jedecId;

masterXfer.dataSize = 4;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

example for reading and programming page in 4 byte mode (32 bit address, after sending 0xB7 opcode):

PRINTF("READ ADDRESS 0X0");

uint8_t page[262];

masterTxData[0] = 0x0B;

masterTxData[1] = 0x0;

masterTxData[2] = 0x0;

masterTxData[3] = 0x0;

masterTxData[4] = 0x0;

masterTxData[5] = 0xFF; //DUMMY BYTE

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = masterTxData;

masterXfer.rxData = page;

masterXfer.dataSize = 262;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_SetDummyData(EXAMPLE_LPSPI_MASTER_BASEADDR, 0xFF); // Set dummy data to 0xFF

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

PRINTF("WR EN");

masterTxData[0] = 0x06;

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = masterTxData;

masterXfer.rxData = NULL;

masterXfer.dataSize = 1;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

PRINTF("PROGRAM ADDRESS 0X0");

uint8_t progpage[267];

int i;

for( i=5;i<267;i++)

{

progpage[i] = i - 5;

}

progpage[0] = 0x02;

progpage[1] = 0x0;

progpage[2] = 0x0;

progpage[3] = 0x0;

progpage[4] = 0x0;

/*Start master transfer, transfer data to slave.*/

masterXfer.txData = progpage;

masterXfer.rxData = NULL;

masterXfer.dataSize = 262;

masterXfer.configFlags =

EXAMPLE_LPSPI_MASTER_PCS_FOR_TRANSFER | kLPSPI_MasterPcsContinuous | kLPSPI_MasterByteSwap;

LPSPI_MasterTransferBlocking(EXAMPLE_LPSPI_MASTER_BASEADDR, &masterXfer);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @adi2Intel,

The LPSPI and FlexSPI modules are inheritably different. As stated by my colleague on the following community post: "the FlexSPI module is dedicated to communicate with Flash-like serial devices. It has a set of dedicated features (like LUT command sequences) for such type of accesses. For SPI communication with a "generic" (non-Flash) SPI devices, the LPSPI module should be used."

As you mention, the BTB examples are meant to show a generic SPI communication between two boards. If you are looking for a standard SPI communication example (not between two boards) refer to the "lpspi_interrupt" example.

BR,

Edwin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can we use the LPSPI to read and write a flash device device using single SPI protocol?

or even use the LPSPI to read JEDEC ID?

basically our device using the flexSPI port to read and write another flash device , and our device has 4 LPSPI ports .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @adi2Intel,

From the W25Q32JV Datasheet: "The W25Q32JV supports the standard Serial Peripheral Interface (SPI)", so it is possible. As mentioned on your previous post, a good example to refer to for LPSPI read/write with NOR Flash would be the "flashloader" example under "bootloader_examples". With the right modifications to the LUT table, you should be able to communicate with the NOR Flash without issues.

BR

Edwin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Edwin

I was able to communicate with the FLASH device using the example for the "lpspi_polling_master"

it was an issue of voltages and power.

example for reading status register: