- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: i.MX RT1170: how to design with PSRAM ( Xccela protocol )

i.MX RT1170: how to design with PSRAM ( Xccela protocol )

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

i.MX RT1170: how to design with PSRAM ( Xccela protocol )

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We'd like design with Xccela protocal PSRAM on i.MX RT1170 platform.

We found i.MX RT1170 have two controller:

FlexSPI1: dual-channel x4 bit,support individual x4 mode , parallel x8 mode;

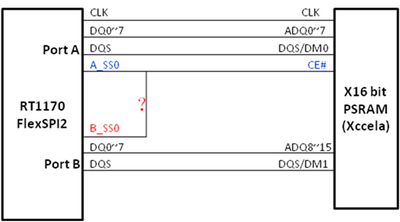

FlexSPI2:dual-channel x8bit, support individual x4/x8 mode,parallel x8/x16 mode;

1. We'd like use FlexSPI2 connect the x8bit Xccela PSRAM, and worked at individual x8 mode.

Whether NXP can well support the above use?

2.If we use FlexSPI2 connect a x16bit Xccela PSRAM(only one CE#),and connect the A_ss0 and B_ss0 both to PSRAM CE#(x16bit PSRAM only have one CE#),Whether it can work properly?

3.What is the maximum clock supported by FLexSPI?200MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am a hardware designer,

I remember a problem that arose when I thought about using an octal flexram for my infotainment application. I was excited about the idea of making a board with few layers for my application. However we found that there is a limit to the size of some buffers inside the flexspi controller in either direction so my idea was not suitable for video application. Maybe the flexspi controller was adequate to control ROM and less suitable for RAMs. I 'd be interested to know if some limits have been exceeded. I don't remember any other details about it. Hi!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Whether NXP can well support the above use?

-- To be prudent, I was wondering if you can upload the datasheet of the Xccela PSRAM.

2) 3.What is the maximum clock supported by FLexSPI?200MHz?

-- The maximum clock frequency is 166 MHz.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

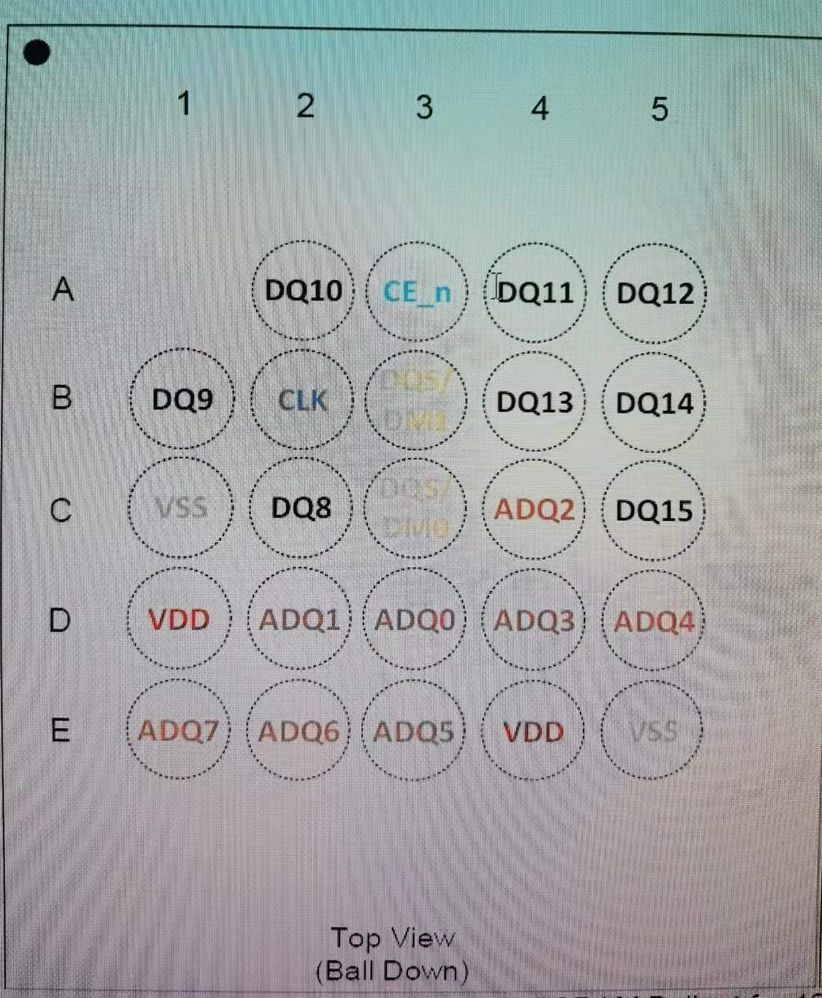

1. please refer to the attachment about the x8bit Xccela PSRAM.

2. i.MX RT600 FlexSPI support CLKmax=200MHz?

3. If we use i.MX RT1170 FlexSPI2 connect a x16bit Xccela PSRAM(only one CE#),and connect the A_ss0 and B_ss0 both to PSRAM CE#(x16bit PSRAM only have one CE#),Whether it can work properly?

x16bit Xccale PSRAM pin:one CE#

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

1) i.MX RT600 FlexSPI support CLKmax=200MHz?

-- Yes.

2) If we use i.MX RT1170 FlexSPI2 connect a x16bit Xccela PSRAM(only one CE#),and connect the A_ss0 and B_ss0 both to PSRAM CE#(x16bit PSRAM only have one CE#),Whether it can work properly?

-- In my opinion, it's available to do that.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

the new x16bit PSRAM: only one CE# pin, and no RST# pin.

1.Is the following design ok?

x16bit PSRAM only uses low byte(ADQ0~7) to access CMD, but FlexSPI2 send CMD on portA and portB individually, whether the CMD send on port A and B are synchronized?

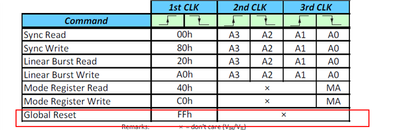

2. x16bit PSRAM uses the global reset CMD to reset the chip, no RST# pin.

Whether the FlexSPI2 supports the global reset CMD?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We look at your case and we believe it should work.

However we can't find any Board in Lab capable to test it.

In case you or NXP team could simulate it, we can support verilog model of 256Mb (APS256XXN-OBR-BG) or 512Mb (APS512XXN-OBR-BG) OPI x16

If you try it, we are very much interested to get your feedback.

Thanks

Alex