- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX论坛

- :

- i.MX RT 交叉 MCU

- :

- Re: When will FlexSPI IPTX/RX DMA request get activated?

When will FlexSPI IPTX/RX DMA request get activated?

Hello,

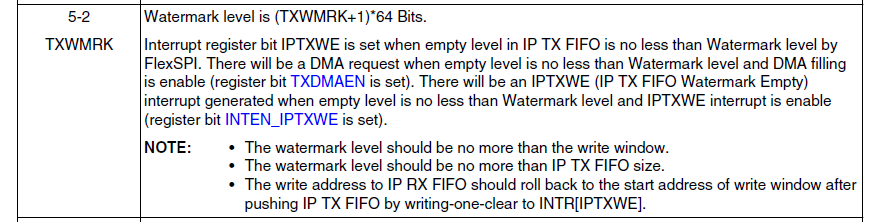

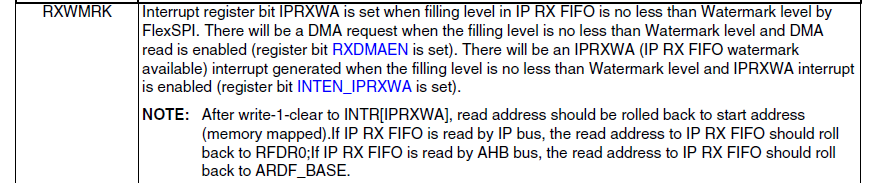

in the RT1020 reference manual you can find the following explanations for FlexSPI IP TX/RX watermark levels

- What does "DMA request whenn filling level is no less than Watermark level" mean? And why is the description for TX/RX the same? Shouldn't it be something like "if TX FIFO count is less or equal to TXWMRK a DMA request will be generated" and for RX "if RX FIFO count is equal or greater than RXWMRK a DMA request will be generated".

- When will DMA request be generated?

- What is a write window?

Kind regards,

Stefan

已解决! 转到解答。

Hi Stefan,

Sorry for the confusion. Your understanding is correct, if there are more than watermark bits free the DMA request will be triggered. "empty level" does mean how many FIFO entries are free.

Regards,

Victor

Hello Stefan,

What does "DMA request when the filling level is no less than the Watermark level" mean?

When will the DMA request be generated?

In the case of TXWMRK, the DMA request will be triggered when the TX FIFO exceeds the Watermark. For the RXWMRK, the DMA request will be triggered when the RX FIFO exceeds the Watermark level. In both cases, DMA filling has to be enabled.

What is a write window?

I'm checking this with the applications team, I will give you an update as soon as possible.

Regards,

Victor

Hello Victor

thank you for answering and checking with the applications team.

Does exceed for TX mean "if there are less than watermark bits in FIFO trigger DMA request"?

or does it mean "if there are more than watermark bits in FIFO trigger DMA request"?

The second option does not make any sense to me because if I trigger a DMA request every time there are more than tx watermark bits in FIFO I will fill the FIFO more and more until I overrun TX FIFO size.

Kind regards,

Stefan

Hello Stefan,

Does exceed for TX mean "if there are less than watermark bits in FIFO trigger DMA request"?

or does it mean "if there are more than watermark bits in FIFO trigger DMA request"?

It means that if there are more than watermark bits in the FIFO the DMA request will trigger. The DMA trigger request will trigger as soon as the FIFO level exceeds the watermark.

What is a write window?

The write window is total size of TX FIFO Data Register (TFDR0 - TFDR31), or total size of AHB Memory Map for TX FIFO write access.

Regards,

Victor

Hi Victor,

sorry for the late reply.

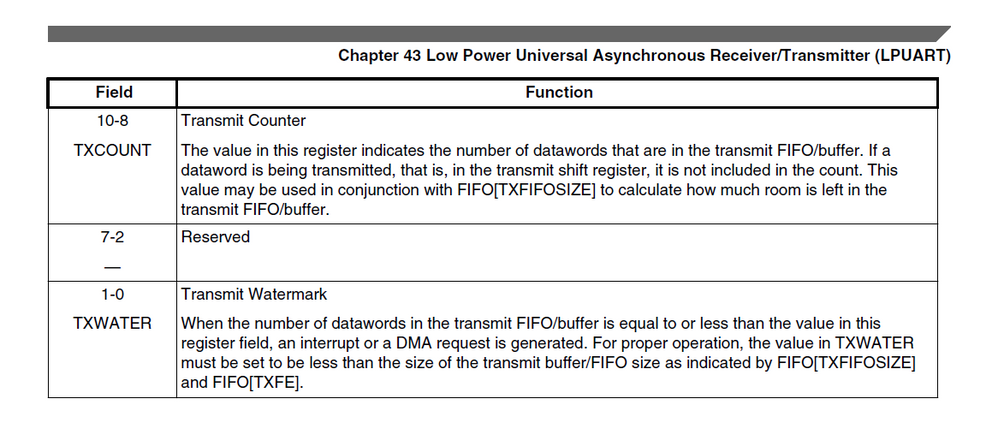

I am confused by the wording of the Reference Manual because the LPUART defines this

If I set my TXWATER to 2 and there is only one element in FIFO the LPUART will trigger a DMA transfer.

If I use this description for the FlexSPI it will be like if there are 3 elements in FIFO but TXWATER is set to 2 it will trigger a DMA transfer which will fill the FIFO even more -> generates another DMA request because there are still more than 2 elements in the FIFO. This would fill the FIFO until an overrun occurs.

If the FlexSPI is defined as if there are more than watermark bits free the DMA request will be triggered it makes sense for me. Does the FlexSPI "empty level" mean how many FIFO entries are free?

Kind regards,

Stefan

Hi Stefan,

Sorry for the confusion. Your understanding is correct, if there are more than watermark bits free the DMA request will be triggered. "empty level" does mean how many FIFO entries are free.

Regards,

Victor