- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MX RT クロスオーバーMCU

- :

- Re: How to put whole .o object in ITCM

How to put whole .o object in ITCM

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

How to put whole .o object in ITCM

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

I am using RT1060 with MCUXpresso IDE 11.0.1 and checked AN12437 i.MX RT Series Performance Optimization application note to learn about how to put instructions in ITCM using AT_QUICKACCESS_SECTION_CODE, but this is function by function.

Is there any way to put all of functions in a single source code/object file into ITCM?

Thanks,

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

There are many, many responses to this question, and there are many, many issues arising.

BUT going back to your first question, you want to place all code (.text*) from a C source module into ITCM. That is very easy to achieve, using the linker file.

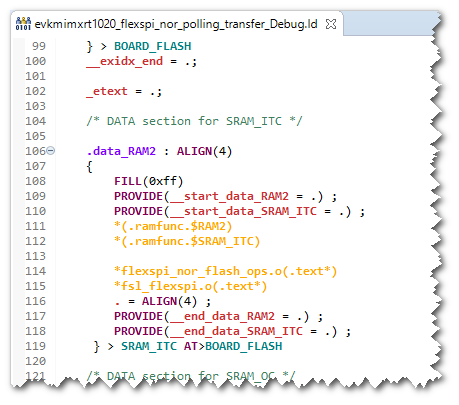

Take a look at the v2.7.0 SDK example project evkmimrt1020_flexspi_nor_polling_transfer (I assume it is the same for your RT1060 equivalent in your SDK). The project is linked for XIP execution from flash, and then erases and programs the flash memory. Obviously the code cannot be running from flash, and so all of the functions from driver API module fls_flexspi.c and flexspi_nor_flash_ops.c are placed into ITCM (that is SRAM_ITC alias RAM2 in this project) by the linker. But the main() is located in flash.

Does this help you?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please check my new updated information under this link:

I still don't have time to double check it, please help to test it on your side at first.

Any updated information, please kindly let me know.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kerry,

That didn't work, and I don't think that workaround works.

If the issue is because of the push instruction at the very first of ResetISR, SP is pointing at 0x20040000 which is nothing assigned at that time. FlexRAM is not configured yet, but the push instruction access to 0x2003FFFC and 0x2003FFF8.

The workaround doesn't help to solve this issue since SP is already pointing at 0x20040000.

Now I understand why debug mode works. The script changes FlexRAM configuration before loading the software, so when it comes to execute the very first push, RAM is already mapped at 0x20040000.

Is there any way to prepare ResetISR without the push?

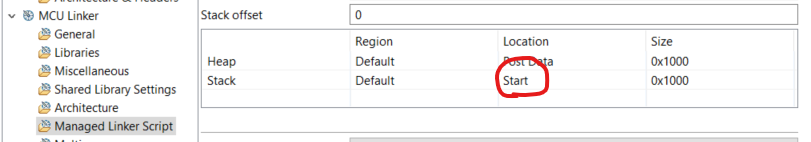

I found how to change the stack location on the IDE. The default value is 'End' but I can set 'Start' so that the stack is at 0x20010000 which is always available. Is there any side effect to change the location from 'End' to 'Start'? With this modification, it is working now.

Thanks,

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi kerryzhou, takashi.kashiwagi@teac.jp,

Is there any side effect to change the stack location from 'End' to 'Start'?

Thanks,

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tom Inoue,

Thanks for your updated information, and let me know the result.

Sorry for my later reply!

In the past days, our IDE expert is in the holiday, then I can't contact with him, now he is back now, I will give the detail test result to him and seek more help.

Any updated information, I will let you know.

Thanks a lot for your understanding.

Best Regards,

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I have reproduced your problems, I will do more research, please wait patiently, thank you!

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you Kerry-san.

Hi Inoue-san.

Please modify the connect script as Kerry-san says in the following thread.

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you, Kerry.

Hi Kashiwagi-san,

On that thread, the processor is RT1052 instead of 1062 and the memory size is different from what I want. So I modified the script as below and it worked with debugger.

But the issue is, it doesn't work without debugger.

360 REM ====== Configure FlexRAM ====== https://community.nxp.com/thread/517877

370 print "Configure FlexRAM for 0KB OC RAM (+dedicated 512KB), 256KB I-TCM, 256KB D-TCM"

380 REM TCM CTRL Poke 0x400B0000 - to force RAM clocking and set wait states = b100

390 Poke32 this 0x400B0000 0x4

400 REM IOMUXC_GPR17 0x400AC044 - this sets bitfield allocation of FlexRAM 32KB banks to OC 256KB b01, I 128KB b11, D 128KB b10

410 Poke32 this 0x400AC044 0xAAAAFFFF

420 REM IOMUXC_GPR16 0x400AC040 - this sets enables for I and DTCM and the source of the TCM config = 0x200007

430 Poke32 this 0x400AC040 0x200007

440 print "Finished"

450 REM ===============================

I guess this is the code to do the same with the script above, so I put this in RestISR, but didn't help.

FLEXRAM->TCM_CTRL = 4;

IOMUXC_GPR->GPR17 = 0xAAAAFFFFu;

IOMUXC_GPR->GPR16 = 0x200007;

This is the previous code I used.

IOMUXC_GPR->GPR17 = 0xAAAAFFFFu;

IOMUXC_GPR->GPR14 &= ~IOMUXC_GPR_GPR14_CM7_CFGDTCMSZ_MASK;

IOMUXC_GPR->GPR14 |= IOMUXC_GPR_GPR14_CM7_CFGDTCMSZ(9); /** DTCM 256KB */

IOMUXC_GPR->GPR16 |= IOMUXC_GPR_GPR16_INIT_DTCM_EN_MASK;

IOMUXC_GPR->GPR14 &= ~IOMUXC_GPR_GPR14_CM7_CFGITCMSZ_MASK;

IOMUXC_GPR->GPR14 |= IOMUXC_GPR_GPR14_CM7_CFGITCMSZ(9); /** ITCM 256KB */

IOMUXC_GPR->GPR16 |= IOMUXC_GPR_GPR16_INIT_ITCM_EN_MASK;

IOMUXC_GPR->GPR16 &= ~IOMUXC_GPR_GPR16_FLEXRAM_BANK_CFG_SEL_MASK;

IOMUXC_GPR->GPR16 |= IOMUXC_GPR_GPR16_FLEXRAM_BANK_CFG_SEL(kFLEXRAM_BankAllocateThroughBankCfg);

I appreciate your help for supporting me, but now it is working with debugger and it doesn't without debugger, so it is difficult to debug more, I think. If you have any suggestions, please let me know. Otherwise, I think I just need to use the default RAM assignment.

Thanks,

Tom Inoue

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tom,

If you want to modify the FlexRAM, I think you can modify the fuse related bit, then even you without debugger, you also don't need to modify the related register in the code, do you mind to modify the FlexRAM fuse to your designed configuration?

Anyway, I will test it on my side with and without the debugger.

Any updated information, I will let you know.

Best Regards,

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kerry,

As you mentioned before, fuse area just can be modified one time, so I don't want to modify that at this moment. Thank you for working on this.

Thanks,

Tom Inoue

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I totally understand you don't want to burn the fuse now.

I still need more time to find the way about the issue after downloading.

Please keep patient!

Best Regards,

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi kerryzhou san

The same phenomenon as the following thread appears.

Can you tell me if you know any solution?

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I just get the project, and will test it which is shared in that post, and give reply later.

Please give me more time, thanks.

After I test it, I will also let you know.

Best Regards,

Kerry

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Inoue-san,

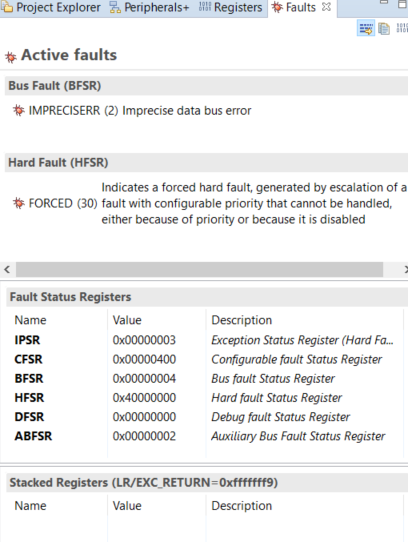

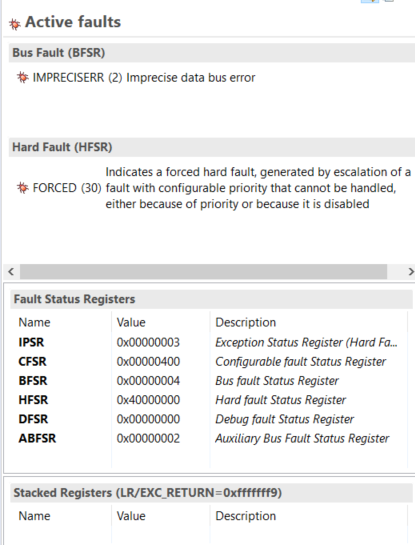

According to ABFSR, Asynchronous fault on DTCM interface has been occurred.

3.3.9. Auxiliary Bus Fault Status Register ARM Information Center

Please check which instruction caused Hard Fault when you executed "step in".

Is the instruction trying to write to an invalid address?

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kashiwagi-san,

I am not quite sure if there is any difference between Step Over and Step Into here since the very first instruction is this:

__asm volatile ("cpsid i");

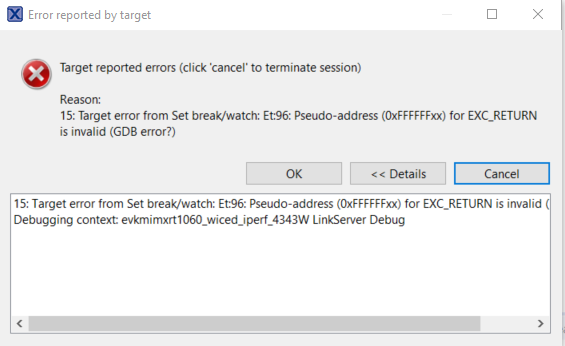

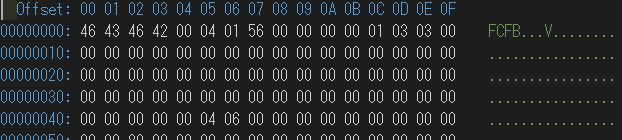

I did Step Into (F5) on that and got the same Hard Fault with additional window as below.

Thanks,

Tom Inoue

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Inoue-san.

I am not quite sure if there is any difference between Step Over and Step Into here since the very first instruction is this:

__asm volatile ("cpsid i");

Does it mean that a hard fault occurs just by executing "__asm volatile ("cpsid i") ;" in your project?

I think that there is no possibility of a hard failure because you can run the "hello world" example ".

So I think that the program is not written correctly.

As a confirmation again, are the PC and SP at the time of break in ResetISR set to the intended values?

Best Regards.

T.kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Inoue-san.

Do you see any issue on my section table?

No. I think there is no problem with the section table.

It seems that the data is not written correctly in FlashROM.

Please compare the binary file with the read memory. And First, check whether the DCD table and the vector table are written correctly. If a DCD table is included, the ROM starts with "FCFB".

If no binary file has been generated, enable the next line in the post-build step.

arm-none-eabi-objcopy -v -O binary "${BuildArtifactFileName}" "${BuildArtifactFileBaseName}.bin"

Best Regards,

T.Kashiwagi

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Kashiwagi-san,

After loading "hello world" example, I could use Debug Mode only one time.

Below is what I can see on the debugger. This matches with the .bin file.

0x60000000 46 43 46 42 00 04 01 56 00 00 00 00 01 03 03 00 FCFB...V........

0x60000010 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

0x60000020 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

0x60000030 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

0x60000040 00 00 00 00 00 04 06 00 00 00 00 00 00 00 00 00 ................

0x60000050 00 00 80 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

0x60000060 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

0x60000070 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

0x60000080 EB 04 18 0A 06 32 04 26 00 00 00 00 00 00 00 00 ë....2.&........

0x60000090 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 ................

Thanks,

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I could put breakpoint on ResetISR. When I start the debugging, Eclipse shows green highlight on this line:

__asm volatile ("cpsid i");

I could do step over with "hello world" example, but I could't with my project. After clicking "step over" button once, Eclipse shows this.

Any suggestion to try something?

Thanks,

Tom

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Tomohiro Inoue,

Thanks for the reply from T.Kashiwagi.

Now, add some comment about your 5 question.

2. Static configuration says FUSE FlexRAM bank configuration. Is this really using Fuse so that this can be done only one time and you cannot change the configuration?

Answer: Just as T.Kashiwagi has replied you, you can use IOMUXC_GPR_GPR17 register to modify the configuration in run time.

But after boot, the configuration will use the fuse data, but please note, fuse area just can be modified one times. So, normally, in your design phase, you can modify the register to realize it, but in the product phase, you can modify the fuse.

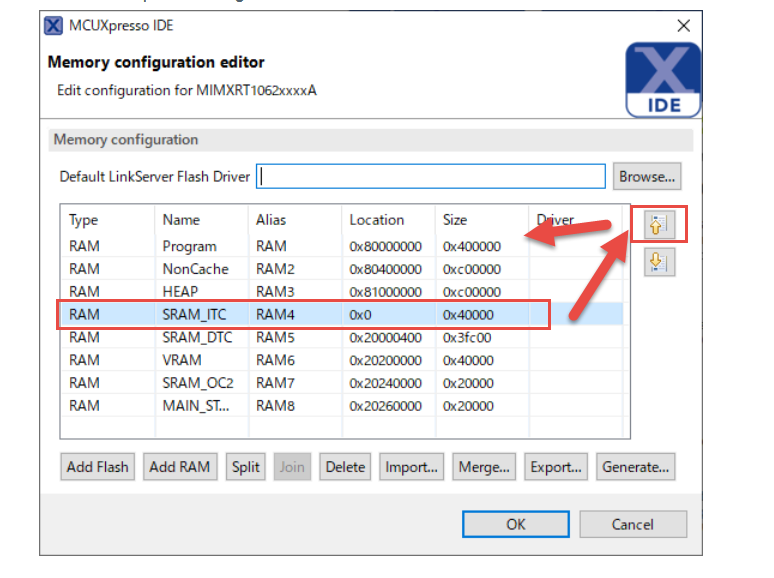

5. I learned from MCUXpresso_IDE_User_Guide.pdf that I can put those object on SRAM_DTC. Can you let me know how I can put those objects on SRAM_ITC using .ldt files? If I modify main_data.ldt, then everything goes to SRAM_DTC, but I would like to use SRAM_ITC since this is instruction code.

Answer:

If you want to use the SRAM_ITC, you can move the SRAM_ITC to the first one in memory configuration editor.

You can try it on your side.

If you still have questions about it, please kindly let me know.

Have a great day,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------