- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- Re: Differences of watchdog peripherals

Differences of watchdog peripherals

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Differences of watchdog peripherals

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi i.MXRT experts,

according to the fact-sheet https://www.nxp.com/docs/en/fact-sheet/IMXRTPORTFS.pdf, the i.MXRT devices have four watchdogs. (In the datasheets for the i.MXRT1010 and i.MXRT1050 I only find three.) However, there are at least WDOG1, WDOG2 and (RT)WDOG3.

Questions:

1) What are the main differences between those both watchdog types? (I know that RTWDOG has a window mode.)

2) How should they be used in a typical application?

3) Is it correct that WDOG1 and WDOG2 need some external circuitry to restart the controller after they have triggered?

4) The RTWDOG has no outputs which can be mapped on any pin/ball. Can the RTWDOG restart the controller by its own?

Thank you for some good feedback!

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Scotty,

Hope you are doing well.

To answer your questions:

1. WDOG1 /2 support two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the Arm core, and a second point evokes an external event on the WDOG line. The third is the RTWDOG provides a safety feature to ensure software is executing as planned and the CPU is not stuck in an infinite loop or executing unintended code. Windowed refresh mode is supported as well. The fourth is the EWM which is designed to monitor external circuits, as well as the software flow. The EWM differs from the internal WDOG in that it does not reset the system. The EWM, if allowed to time-out, provides an independent trigger pin that when asserted resets or places an external circuit into a safe mode. For more details please review the dedicated chapters in the reference manual.

2. The concept is the same for all three as they are safety mechanisms to prevent it form getting stuck. I'd recommend to look at the features listed in the three chapters for each watchdog type as well as the clock sources to see which is the best fit for your application.

3. Yes, it does reset. Please refer to the system reset controller for the Watchdog3 Time-out reset. If you need external signals then please use the External Watchdog Monitor(EWM) as this has two external signals.

i.MX RT1050 Processor Reference Manual

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sabrina,

thank you for the prompt response. - I hope that you are also doing well.

I am only concerned about the WDOG1/2 and (RT)WDOG3, not the EWM.

Is your 3. answer really the response to my 3. question? (You refer to WDOG3 but the question is about WDOG1/2)

Please also notice that I asked a 4. question.

To make my 3. questions more concrete:

I have an application where I activated WDOG2. The output is not routed to an external pin. If WDOG2 is not serviced, I can see that the timer expires and the timeout flag is set. But nothing more happens! So, it does *not* reset the CPU. I assume that the reset / restart only works by connecting the watchdog output to some external reset circuit. Or am I wrong?

Please can you clarify your answers.

Best regards,

Michael a.k.a. Scotty

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I apologize it seems I missed the third question. So the number 3 in my answer is to your fourth question.

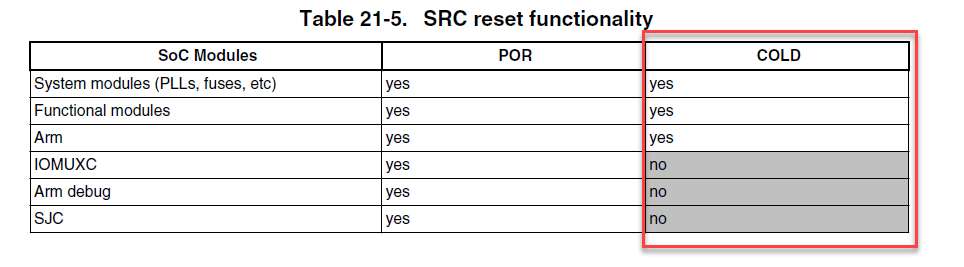

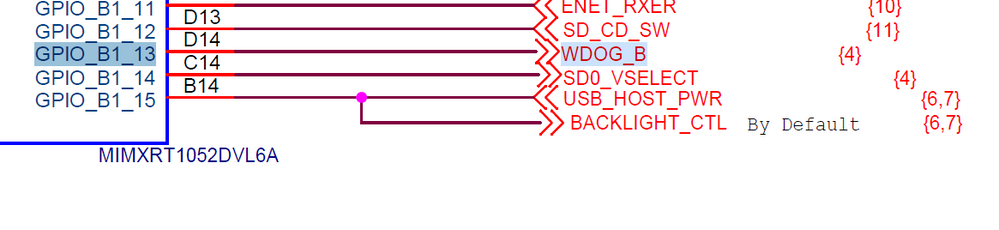

For 3. It does offer external pins to connect externally. You may refer to wdog1_b and wdog2_b, however it is not necessary unless you would like to do a POR and want to trigger an external reset for the chip.

The WDOG1 asserts the internal system reset signal, WDOG_RESET_B_DEB to the System Reset Controller

(SRC); and WDOG2 asserts interrupt to SNVS, to report the security violation condition.

The WDOG_RESET_B_DEB is of type Cold.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sabina,

do you have a complete example which shows how to configure the WDOG3 (incl. clock, SCR, mux setup if needed)?

My investigations were based on the snippet I found in the reference manual (see below). But as I said: it stops the application but does not restart it.

Regards,

michaeL

DisableInterrupts; //disable global interrupt

WDOG_CNT = 0xD928C520; //unlock watchdog

while(WDOG_CS[ULK]==0); //wait until registers are unlocked

WDOG_TOVAL = 256; //set timeout value

WDOG_CS = WDOG_CS_EN(1) | WDOG_CS_CLK(1) | WDOG_CS_INT(1) |

WDOG_CS_WIN(0) | WDOG_CS_UPDATE(1);

while(WDOG_CS[RCS]==0); //wait until new configuration takes effect

EnableInterrupts; //enable global interrupt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hope you are doing well.

I will check with our application team in regards to the B and DEB of the two signals. As far as I am aware the B and DEB differentiate between external and internal signals.

You may refer to the examples provided in the SDK.

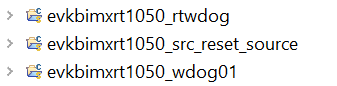

There is examples for WDOG1, RTWDOG as well as the SRC.

Please refer to these examples for the correct configurations.

Could you please confirm where you are seeing the following:

The relating bits for "Wdog3 reset mode configuration" (WDOG3_RESET_MODE) are b00 which means "reset system".

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sabina,

yes, it would be nice if you could ask further experts. The block diagram figures in the reference manuals are helpful. But it is not clear to me which signals are interal and which can be routed to a pin.

I checked the example code though the final application will not use the i.MXRT1050, but a newer one which is already referred to in the fact sheet I mentionen above (https://www.nxp.com/docs/en/fact-sheet/IMXRTPORTFS.pdf).

For the I.MXRT1050 the "SRC Control Register" contains the configuration "mask_wdog3_rst" which is b1010 by default and should enable WDOG3 to reset the controller.

Best Regards,

Michael

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Michael,

Hope you are doing well.

As for the name endings on this signal, this was a decision made by the designers and unfortunately I do not have the information as to why it is _b and _b_deb. As stated previously the _b can be routed to external pins while the _b_deb is an internal signal that may be asserted for the reset. Please keep in mind that the reset is a "COLD" reset, so it does not have all the reset functionalities as a POR reset. If you need to cause an entire system reset then you should use the external pin when using WDOG1.

For the information on POR vs COLD reset types please refer to the reference manual.

In section 9.5.2 of the reference manual you may see that the watchdog timer is configured by boot ROM. So we do not have access to these configurations. However, if you would like to verify that it is being reset internally you can take the wdog 1 example and take the pin that is routed on our EVKB.

Change the configuration prior to the resets, such as GPIO input. Then you will see that in the example this is still being reset after a watchdog timeout. I understand that you will use another micrcontroller. I'd recommend seeing the examples through that microcontroller as the information is not public and I do not have access to verify if the behavior is the same across these two RT modules.

Best Regards,

Sabina

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you, Sabina, for your further explanations.

In the mean time I managed it to let WDOG1 reset my system with the help of an external reset controller. For this, I configured the I/Omultiplexer so that WDOG1_B is routed to the specific pin.

But I could not manage it that WDOG1 (or RTWDOG3) restarts the controller without the external pin. I only see that the firmware stops and does not restart.

The SRC is a good hint. Maybe I missed there some configurations.

Do I need to tell the SRC that it should restart the controller on watchdog timeouts?

This question is also essential for RTWDOG3 which it does not have external outputs.

Futher questions which may help to understand the watchdog peripherals:

- For what does the B stand in WDOG1_B?

- For what does the DEB stand in WDOG1_RST_B_DEB?

Best regards,

Michael

---

Update / Edit:

I found the register "SRC Control Register" (SCR) within the register range of the System Reset Controller.

The relating bits for "Wdog3 reset mode configuration" (WDOG3_RESET_MODE) are b00 which means "reset system". So, this should not be the reason that the controller does not restart on WDOG3 timeout events.