- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX RT Crossover MCUs

- :

- DCD on iMXRT1021

DCD on iMXRT1021

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

All,

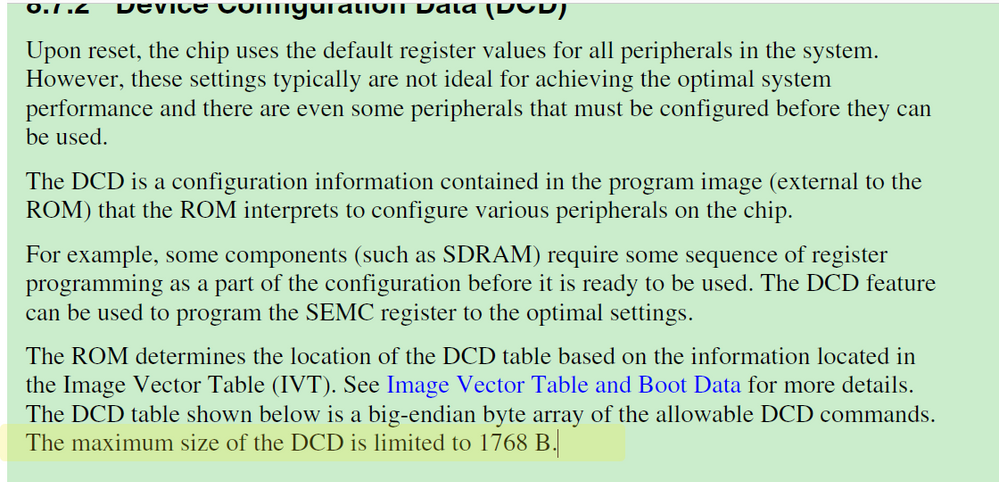

We are having problems with the DCD on the iMXRT1021. The problem is with the documentation, so we have some questions:

1. Both the RT1020 Reference Manual and the RT1050 Security Reference Manual mention in the Note for the DCD Write Command that any target address outside of the allowed region cause the whole command to be invalidated. They also promise a list of allowable blocks and target addresses, but these don’t appear anywhere in the documents. We need a list of allowed regions for the RT1021

2. Are the Watchdog1 registers in these allowed regions?

3. The MCUXpresso Config Tool gives a small list of allowed registers, and when I enter an ITCM address (0x0000F000 in this case) says that it is not allowed. However, when actually implementing a DCD Write Command to this address it successfully completes. Is RAM different to Peripheral Register addresses?

4. What happens if an individual command specifies a number of bytes that exceeds the total DCD size?

Thanks,

Chris.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi chriscowdery,

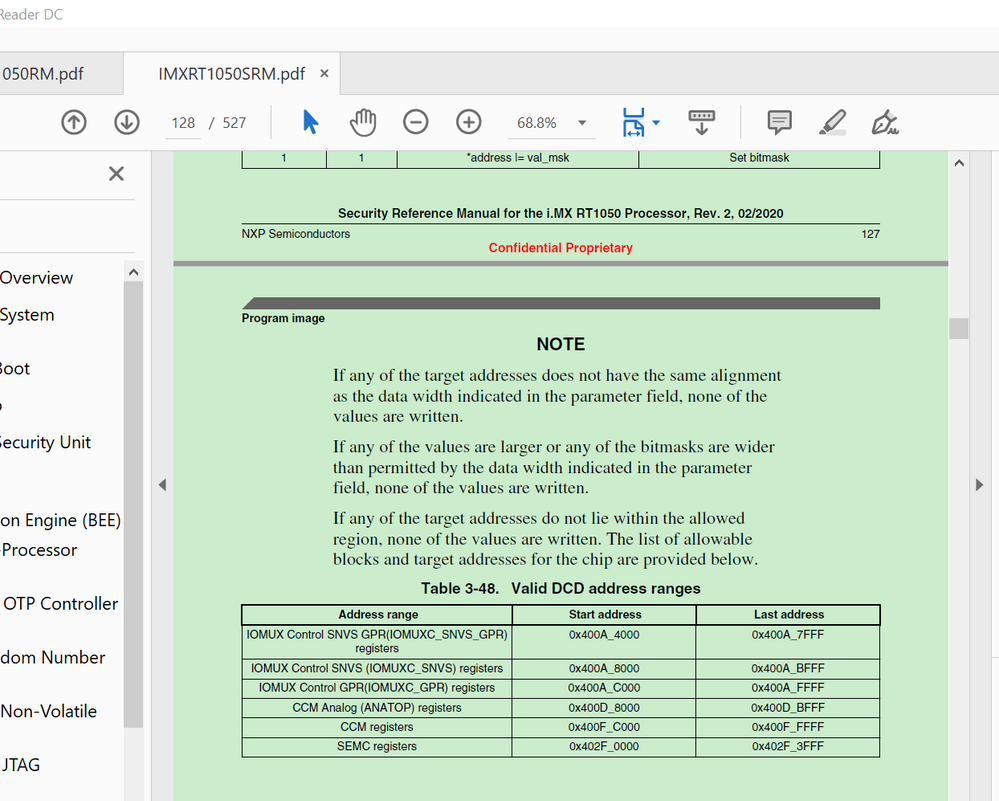

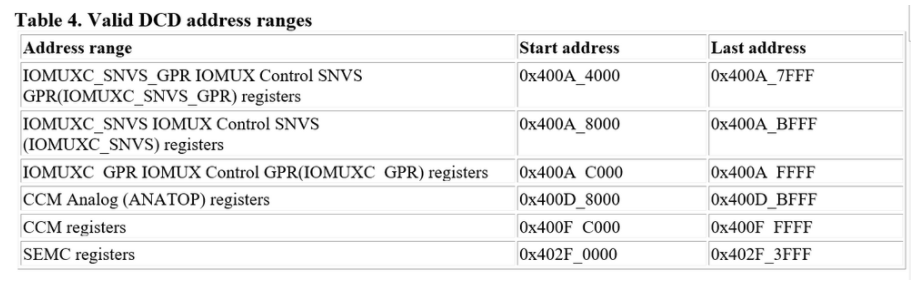

1, The picture which I share with you is from the RT1050SRM:

2. The table does not show any RAM? Does this mean the DCD cannot access any RAM region?

Answer: Yes, DCD need to use the valid address range in the table.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-----------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Kerry,

Thankyou. Two followup questions:

1. Where is the table you show for answer #2 ? Which document?

2. The table does not show any RAM? Does this mean the DCD cannot access any RAM region?

Thankyou.

Chris.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi chriscowdery,

1, The picture which I share with you is from the RT1050SRM:

2. The table does not show any RAM? Does this mean the DCD cannot access any RAM region?

Answer: Yes, DCD need to use the valid address range in the table.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-----------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi chriscowdery,

1. Both the RT1020 Reference Manual and the RT1050 Security Reference Manual mention in the Note for the DCD Write Command that any target address outside of the allowed region cause the whole command to be invalidated. They also promise a list of allowable blocks and target addresses, but these don’t appear anywhere in the documents. We need a list of allowed regions for the RT1021

Answer:

2. Are the Watchdog1 registers in these allowed regions?

Answer:

You can find the WDOG is not in the list.

3. The MCUXpresso Config Tool gives a small list of allowed registers, and when I enter an ITCM address (0x0000F000 in this case) says that it is not allowed. However, when actually implementing a DCD Write Command to this address it successfully completes. Is RAM different to Peripheral Register addresses?

Answer:

Please refer to the above picture which I share with you, you need to operate the address in the range.

4. What happens if an individual command specifies a number of bytes that exceeds the total DCD size?

Answer: I think if the size is exceeds, ROM will not copy the code which is out of size.

Wish it helps you!

If you still have questions about it, please kindly let me know.

Best Regards,

Kerry

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-----------------------------------------------------------------------------