- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

im6q - undesire arm clock root frequency

--------------------------------------------------------------------------------------------------

SETTING:

PLL_ARM divider set to 16, Clock divider set to 0.

Thus, ARM clock root = 24 / 2 * 16 / ( 0 + 1)

= 192 Mhz

--------------------------------------------------------------------------------------------------

CODE:

while(1){

counter++;

if (counter >= 0x40000000){ // if counter >= 1 Giga

toggleGPIOPIN();

resetCounter();

}

}

--------------------------------------------------------------------------------------------------

FOR 'counter++' part, 3 line assembly code is generated by the compiler:

LOAD

ADD

BRANCH

--------------------------------------------------------------------------------------------------

Thus at least 3 clock cycle for the 'counter++' loop.

Time between GPIO PIN toggle should be at least = (3 x 1 Gig) / 192 Meg

= 15.625 second

BUT the problem occur. Time between GPIO toggle is ~5 second (measure by oscilloscope)

Means the arm clock root running at least = 5 / (3 x 1Gig)

= 600 Mhz

--------------------------------------------------------------------------------------------------

I did try to set arm clock root to 800Mhz, but the result shows it run more then 2GHz.

WHAT IS HAPPENING??

Hi Anson,

if you are speaking about CCM_ANALOG_PLL_ARMn

DIV_SELECT can not be 16. Valid range for divider value: 54-108.

Fout = Fin * div_select/2.0.

Sect.18.5.1.3.1 "ARM PLL" i.MX6DQ RM states:

"This PLL synthesizes a low jitter clock from a 24 MHz reference clock. The clock output

frequency for this PLL ranges from 650 MHz to 1.3 GHz. The output frequency is

selected by a 7-bit register field CCM_ANALOG_PLL_ARM[DIV_SELECT].

PLL output frequency = Fref * DIV_SEL/2"

Also it may be useful to check arm clock root

with CCM_CCOSR.

Best regards

chip

I tried your suggestion, clkout result is not correct as well.

--------------------------------------------------------------------------------------------------------------------------------------------------------------

ARM Clock Setting:

PLL_DIV => 54

CLK_DIV => 7

PLL_ARM = 24 * PLL_DIV / 2

= 24 * 54 / 2

= 648 MHz

ARM CLOCK ROOT = PLL_ARM / (CLK_DIV + 1)

= 648 / (7 + 1)

= 81 MHz

---------------------------------------------------------------------------------------------------------------------------------------------------------------

CCM_CCOSR Setting:

CCOSR_DIV => 8

---------------------------------------------------------------------------------------------------------------------------------------------------------------

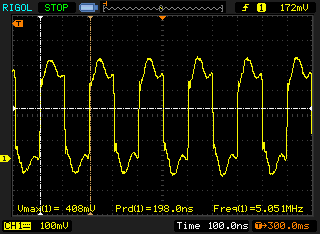

aspected clkout = ARM CLOCK ROOT / CCOSR_DIV

= 81 / 8

= 10.125 MHz

But result measure is = 5.051 MHz

Hi Anson,

what software and board are you using ?

I would suggest to printf all registers for example

(CCM_CACRR) and its "arm_podf' value and others.

All clock generation paths one can find in Chapter 18

i.MX6DQ RM. Even better to use SDK

i.MX 6Series Platform SDK  : Bare-metal SDK

: Bare-metal SDK

Best regards

chip

Hi Anson,

I would suggest to check with SDK

i.MX 6Series Platform SDK  : Bare-metal SDK for the i.MX 6 series

: Bare-metal SDK for the i.MX 6 series

Best regards

chip

CCM_ANALOG_PLL_ARM (Addr: 0x20C_8000) Value: 0x80002036

CCM_CACRR (Addr: 0x20C_4010) Value: 0x7

CCM_CCOSR (Addr: 0x20C_4060) Value: 0x01EA0001

IOMUXC_SW_MUX_CTL_PAD_GPIO03 (Addr: 0x20E_022C) Value: 0x4

Output Measure at: clko2

OS: QNX