- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- iMX RT1024 JTAG and POR_B

iMX RT1024 JTAG and POR_B

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

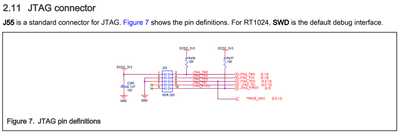

Designing a custom board using RT1024 using the JTAG interface for programming and debugging...

I want to confirm that the JTAG_nTRST connection only connects the JTAG interface header (J55 on EVK) to pin GPIO_AD_B0_05 (pin 106 on 144-pin package). Please confirm that there is no connection of JTAG_nTRST to the POR_B pin (pin 50 on 144-pin package).

-----

Also in regards to the POR pin...

The documentation recommends using a voltage supervisory circuit for asserting POR pin HIGH after internal rails are up and running and that using a simple RC circuit could present issues. Is the issue with the RC circuit that the charge time would be too fast and could assert POR pin HIGH prematurely? Or is it a stability issue?

What is the worst case amount of time it would take for the internal power blocks to stabilize? Would the RC circuit be usable if the delay time is very long (say 100ms or more) to guarantee that even in worst case power-up time the RC would not assert POR to soon?

We will be using an external 1.2V LDO to power the SOC. If we not using the internal DCDC converter, is it possible to just leave POR_B pin disconnected? What circumstances is it OK to not connect the POR_B pin to anything?

Thanks!

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

There is no connection between pin 106 (JTAG_TRSTB) and pin 50 (POR_B). Just keep in mind that POR_B can reset the entire chip including the JTAG module.

For more information I would recommend you to refer to chapter 3 of the Hardware Development Guide and chapter 4.2 of the Data Sheet.

Could you please take a look to the following threads?

https://community.nxp.com/t5/i-MX-Processors/About-POR-B-signal/td-p/510975

https://community.nxp.com/t5/i-MX-RT/I-MX-RT1024-POR-B-pin-is-not-used/m-p/1466102

I hope this helps.

Have a good day!

Daniel.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you for the response. Ok to the JTAG connections.

In regards to the POR_B connection, I am going to use an RC circuit with a 100ms+ charge time and see how that goes. I find it very interesting that the processor was intended to not need a POR_B pin connection but still has a strong recommendation to have it connected to an external circuit.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

There is no connection between pin 106 (JTAG_TRSTB) and pin 50 (POR_B). Just keep in mind that POR_B can reset the entire chip including the JTAG module.

For more information I would recommend you to refer to chapter 3 of the Hardware Development Guide and chapter 4.2 of the Data Sheet.

Could you please take a look to the following threads?

https://community.nxp.com/t5/i-MX-Processors/About-POR-B-signal/td-p/510975

https://community.nxp.com/t5/i-MX-RT/I-MX-RT1024-POR-B-pin-is-not-used/m-p/1466102

I hope this helps.

Have a good day!

Daniel.