- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

We have interfaced an Audio DAC to i.MX53 controller trough the SSI interface in I2S mode for the audio playback output.

The Audio DAC is from Wolfson WM8523. This particular DAC doesn't have any internal PLL and needs an accurate external Master clock input to produce the accurate Sampling rates for the outputs. The Master Clock for the DAC is produced from "CCM_SS1_EXT1_CLK " pin of Controller.

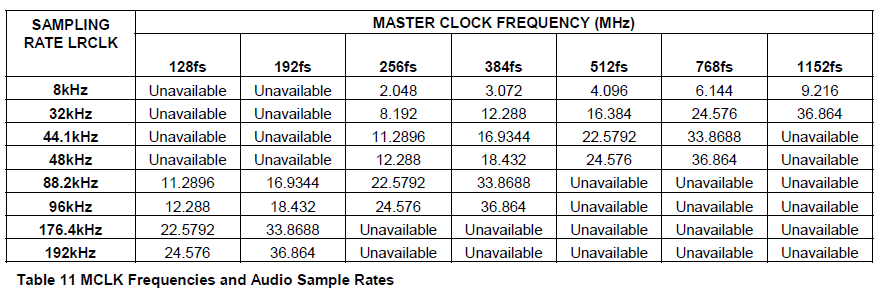

The Master clock requirements are given below,

We needed the sampling rates of 96KHz, hence we were trying to set the Master clock value to 24.576 MHz. When we have set to this value, we are getting 25 MHz. And then when we try to set to 24 MHz, we are getting 23.59 MHz. Also, I have noticed that the Master clock output value is getting rounder off to 24MHz.

I think that there is an issue with the clock output resolution steps. We are able to get only 25 MHz after 23.59 MHz and not any other value in between.

What clock configurations would be required to achieve the above mentioned required Master Clock on CCM_SS1_EXT1_CLK pin??

已解决! 转到解答。

Hello,

i.Mx53 don't provide precise PLL for Audio application.

An external oscillator is required like i.Mx53 SMD reference design.

BTW,Audio Codec also can be acted as sample clock generator.

Gopi

How about your this DI? Had your issue got resolved? If yes, we are going to close the discussion in 3 days. If you still need help please feel free to contact Freescale.

Thanks,

Yixing

Hi,

We couldn't fix this issue on i.mx53 platform (didn't get any response, neither from Freescale email support, nor this forum).

To meet our higher & accurate sampling rate requirements (96KHz & more), we have used hardware PLL module which would provide audio MCLK with variations for different sampling rates.

It is strange why none of the FSL team responded on this till now.

Still no clue about how to achieve the required MCLK to meet the required sampling rates!!

Regards,

Gopi

hello,

Did you manage to make it work ? I'm trying to do the same on imx6q and i would like to know how to set the ssi clock in ssi_imx.c. There is no API for that except adding some code.

I would like to manage 32,44.1, etc. sample rates