- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- a question about IMX8QXP eDMA

a question about IMX8QXP eDMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

a question about IMX8QXP eDMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

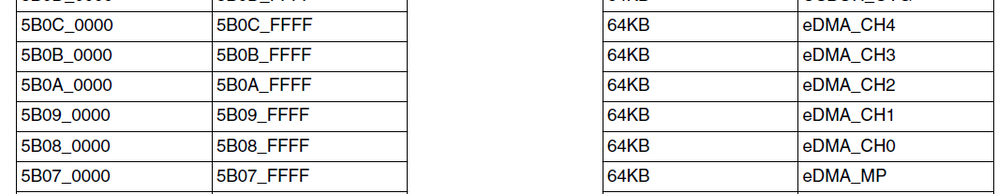

In IMX8DQXPRM(Rev.D 11/2018).pdf I saw register memory map list as below:

This is register map of eDMA in Connectivity subsystem.

My questions are:

a.I can NOT see which peripherals associated with those 5 Connectivity's eDMA channels.

b.What the difference between Connectivity's eDMA and ADMA's eDMAs?

c.If I want to access ADMA's eDMA controller register(0x5a1f0000), which clock domain and gates need to be enabled? now I can access ADMA's eDMA's channel register, but cannot access ADMA's eDMA controller register.

d.Can all those channels perform moving data from memory to memory?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Li

a. one can look at Figure 16-1. Audio Subsystem High-Level Block Diagram,

Table 16-2. eDMAn Channel Map i.MX8QXP Reference Manual

https://www.nxp.com/docs/en/reference-manual/IMX8DQXPRM.pdf

b. one can look at architecture description in Figure 1-1. i.MX 8QuadXPlus/i.MX 8DualXPlus

Simplified Block Diagram, Chapter 14 Connectivity Subsystem

c. for eDMA2((0x5a1f0000) one can check clock control LPCG_EDMA2 descriptions

in Table 8-4. System Clocks, and Gating, sect.8.4 Low Power Clock Gating Control

d. yes

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Igor,

Thanks for your quick reply.

I also have something else not clear:

a.I can see the details about Audio Subsystem eDMA controllers eDMA0~3, but nothing about Connectivity eDMA controller(may be could called eDMA4). Does eDMA4 (0x5b070000~0x5b0cffff) work? Is there no peripherals be associated with those 5 channels?

c. I still meet: In Connectivity, LPCG_EDMA_REGS (0x5b2a0000) can NOT access, but LPCG_RAWNAND_0_REGS(0x5b290000) could.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Li

a. "Connectivity Subsystem" is just another module which has own eDMA module.

> Is there no peripherals be associated with those 5 channels?

please check Figure 14-1. Simplified Block Diagram in Chapter 14

Connectivity Subsystem Reference Manual.

b. one can check eDMA examples in SDK for i.MX 8QuadXPlus (SDK_2.5.0_MEK-MIMX8QX)

available on

Welcome | MCUXpresso SDK Builder

For specific issues with eDMA development may be recommended to proceed with

NXP Professional Services | NXP

Note this part is "Preproduction" as described in red on below link - so there no full support for it.

i.MX 8X Applications Processors| Arm® Cortex®-A35, Cortex-M4 | NXP

Best regards

igor