- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Using RMII(SMSC LAN8720A) on i.MX6solo

Hello,

We use SMSC's LAN8720A as RMII PHY on i.MX6solo and currently having problem with

send & receiving packets(Checking at U-boot).

U-Boot > ping 192.168.100.1

eth_halt: wait for stop regs

eth_halt: done

Trying FEC

fec_tbd_init

Using FEC device

fec_send: status 0x8c00 index 0 ret -22

fec_recv: ievent 0x0

fec_recv: status 0x8000

fec_recv: stop

fec_recv: ievent 0x0

fec_recv: status 0x8000

fec_recv: stop

...

First of all, normally which cause "eth_halt: wait for stop regs" at the beginning?

By looking at code, fec_send function stuck at below two points and return error codes,

| while (--timeout) { | ||

| if (!(readl(&fec->eth->x_des_active) & FEC_X_DES_ACTIVE_TDAR)) | ||

| break; |

}

| if (readw(&fec->tbd_base[fec->tbd_index].status) & FEC_TBD_READY) | |

| ret = -EINVAL; |

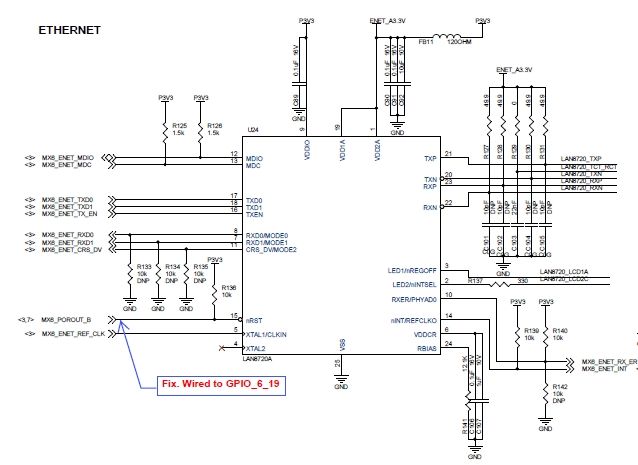

Here's our IOMUX configuration and schematics

Needs help for fix this problem step by step.

iomux_v3_cfg_t const enet_pads[] = {

MX6_PAD_ENET_MDC__ENET_MDC | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_MDIO__ENET_MDIO | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_RXD0__ENET_RDATA_0 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_RXD1__ENET_RDATA_1 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_CRS_DV__ENET_RX_EN | MUX_PAD_CTRL(ENET_PAD_CTRL),

// MX6_PAD_ENET_RX_ER__ENET_RX_ER | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_RX_ER__GPIO_1_24 | MUX_PAD_CTRL(NO_PAD_CTRL),

/* FEC Intterupt */

MX6_PAD_ENET_REF_CLK__GPIO_1_23 | MUX_PAD_CTRL(NO_PAD_CTRL),

MX6_PAD_ENET_TXD0__ENET_TDATA_0 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_TXD1__ENET_TDATA_1 | MUX_PAD_CTRL(ENET_PAD_CTRL),

MX6_PAD_ENET_TX_EN__ENET_TX_EN | MUX_PAD_CTRL(ENET_PAD_CTRL),

/* clock from anatop */

MX6_PAD_GPIO_16__ENET_ANATOP_ETHERNET_REF_OUT | MUX_PAD_CTRL(ENET_PAD_CTRL),

/* LAN8720A PHY Reset */

MX6_PAD_RGMII_TXC__GPIO_6_19 | MUX_PAD_CTRL(NO_PAD_CTRL),

};

Thanks in advance,

Jay

I have exact the same issue.

TX Clock is enabled - (gpr1 bit 21 is set to 1)

Also for the ENET REF CLOCK, SION bit is enabled.

I don't understand what the issue in the dma has todo with the tx clock of the phy?

Hello Jimmy,

So far as I observe, I think yes.

U-Boot > pri ethact

ethact=FEC

U-Boot > pri ethaddr

ethaddr=00:02:BD:AB:CD:EF

U-Boot > md 021880e4 4

021880e4: 0002bdab cdef8808 00010000 00000000 ................

U-Boot > mii info

fec_mdio_read: phy: 00 reg:03 val:0xffff

fec_mdio_read: phy: 01 reg:03 val:0xc0f1

fec_mdio_read: phy: 01 reg:02 val:0x7

fec_mdio_read: phy: 01 reg:00 val:0x3100

fec_mdio_read: phy: 01 reg:05 val:0xcde1

fec_mdio_read: phy: 01 reg:00 val:0x3100

fec_mdio_read: phy: 01 reg:05 val:0xcde1

PHY 0x01: OUI = 0x01F0, Model = 0x0F, Rev = 0x01, 100baseT, FDX

If there's another way to confirm MAC address is properly configured, please let me know to do it.

Whenever I try networking relative commands like dhcp, tftpboot, nfs... etc, symptom is same as

I'd described above executing ping command.

It seems phy/mac have no clock.

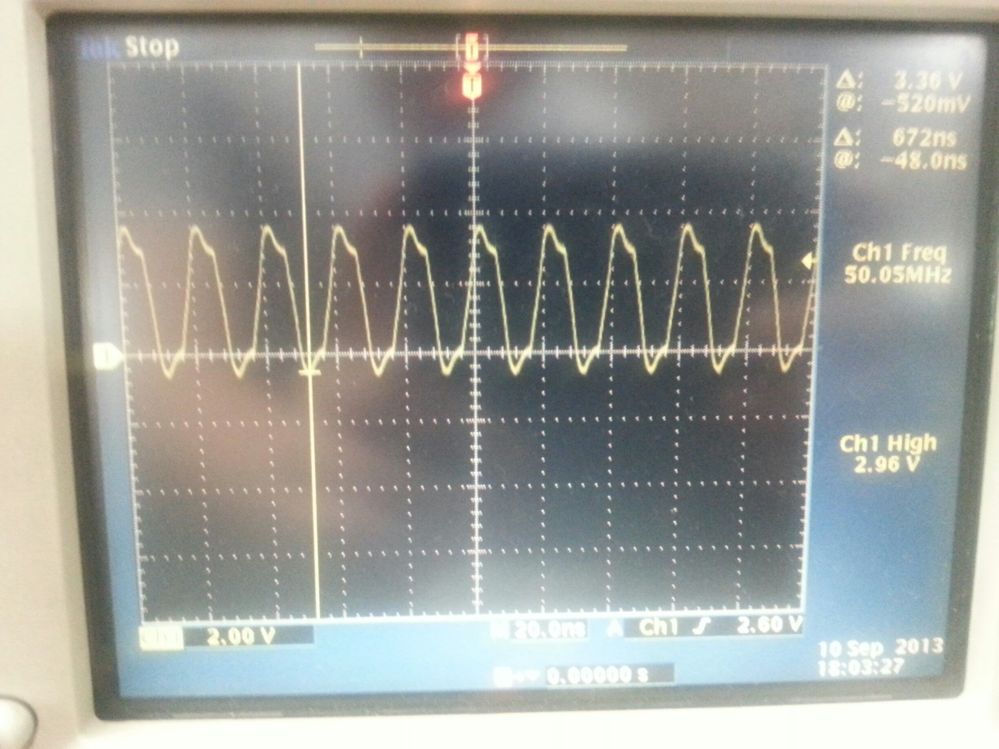

so, 1. Make sure the iomux config for : MX6_PAD_GPIO_16__ENET_ANATOP_ETHERNET_REF_OUT

2. From the info from you attached, the clock is from internal anatop PLL, make sure the clock enable. You can measure the GPIO_16 PAD clock.

Thanks,

Andy

1. It's my iomux pad value

MX6_PAD_GPIO_16__ENET_ANATOP_ETHERNET_REF_OUT = IOMUX_PAD(0x05E4, 0x0214, 2, 0x080C, 0, 0),

2. Attached are measured 50Mhz clock at GPIO_16.

If it seems no problem, isn't there any other possibilities to cause the problem?

Thanks,

Jay

I'm getting the exact same problem on imx6q with a Micrel KS8721BL PHY. I also verified 50MHz clock output on the scope. Please let me know if you've find out what the issue was. Thanks.