- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Setting IMx8MQ Mipi CSI2 clock for OV5640 RAW8 BIT Bayer

Setting IMx8MQ Mipi CSI2 clock for OV5640 RAW8 BIT Bayer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Setting IMx8MQ Mipi CSI2 clock for OV5640 RAW8 BIT Bayer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

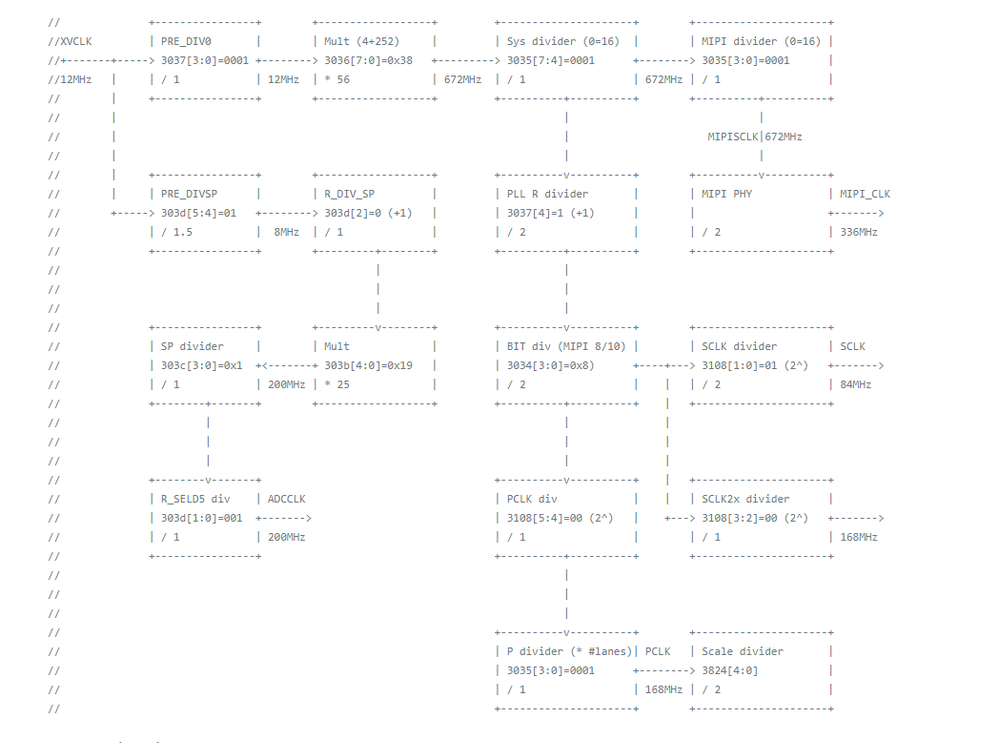

1. From above OV5640 Clock pipeline, we'd like to change MIPISCLK - 672 MHz to 456 MHz ,

then How to setup MIPI CSI2 DPhy Clcok ?

Below is for i.MX6 MPU , how to setup DPHY Clock for i.Mx8M Quad?

do we modify mipi_csi_1: mipi_csi1@30a70000 device tree ?

from https://www.nxp.com/docs/en/application-note/AN5305.pdf

MIPI D-PHY Clock for i.MX6 MPU.

3.4. MIPI D-PHY clock

The camera sensor (the sensor output differential clock) drives and controls the MIPI D-PHY clock.

The MIPI D-PHY clock must be calibrated to the actual clock range of the camera sensor’s D-PHY

clock and the calibrated value must be equal to or greater than the camera sensor clock. This frequency

ranges from 80 MHz to 1000 MHz.

The MIPI D-PHY clock must be set according to a known value of the camera sensor’s pixel clock. This

must be a known value or a value measured with an oscilloscope during a high-speed burst.

To calculate the MIPI data rate, use these equations:

MIPI data rate = (MIPI clock * 2) * Number of lanes >= Pixel clock * Bits-per-pixel

MIPI clock = (Pixel clock * Bits-per-pixel) / (Number of lanes) / 2

For example, a video input of 720p, 59.94 fps, and YUV422 is calculated as follows:

Pixel clock = 1280 * 720 * 59.94 fps * 1 cycle/pixel * 1.35 blank interval = 74.57 MHz

Total MIPI data rate is 74.25 M * 16 bits = 1193 Mb/s.

The frame blank intervals and the interface packaging overhead were added as the 1.35 factor in the

pixel clock equation above.

For a 2-lane interface:

MIPI clock = 1193 / 2 / 2 = 298.25 MHz

MIPI_CSI2_PHY_TST_CTRL1 setting = 298.25 MHz * 2 (DDR mode) = 596.5 MHz

According to Table 2, MIPI_CSI2_PHY_TST_CTRL1 = 0x2E.

For a 4-lane interface:

MIPI clock = 1193 / 4 / 2 = 149.12 MHz

MIPI_CSI2_PHY_TST_CTRL1 setting = 149.12 MHz * 2 (DDR mode) = 298.24 MHz

According to Table 2, MIPI_CSI2_PHY_TST_CTRL1 = 0x28.

-- device tree file --

mipi_csi_1: mipi_csi1@30a70000 {

compatible = "fsl,mxc-mipi-csi2_yav";

reg = <0x30a70000 0x1000>;

interrupts = <GIC_SPI 44 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX8MQ_CLK_CSI1_CORE>,

<&clk IMX8MQ_CLK_CSI1_ESC>,

<&clk IMX8MQ_CLK_CSI1_PHY_REF>;

clock-names = "clk_core", "clk_esc", "clk_pxl";

assigned-clocks = <&clk IMX8MQ_CLK_CSI1_CORE>,

<&clk IMX8MQ_CLK_CSI1_PHY_REF>,

<&clk IMX8MQ_CLK_CSI1_ESC>;

#ifndef PIXEL_RAW

assigned-clock-rates = <133000000>, <100000000>, <66000000>;

#else

assigned-clock-rates = <266000000>, <150000000>, <66000000>;

#endif

/*

assigned-clock-parents = <&clk IMX8MQ_SYS1_PLL_266M>,

<&clk IMX8MQ_SYS2_PLL_1000M>,

<&clk IMX8MQ_SYS1_PLL_800M>;

*/

power-domains = <&pgc_mipi_csi1>;

csis-phy-reset = <&src 0x4c 7>;

phy-gpr = <&iomuxc_gpr 0x88>;

status = "disabled";

};

csi1_bridge: csi1_bridge@30a90000 {

compatible = "fsl,imx8mq-csi", "fsl,imx6s-csi";

reg = <0x30a90000 0x10000>;

interrupts = <GIC_SPI 42 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clk IMX8MQ_CLK_DUMMY>,

<&clk IMX8MQ_CLK_CSI1_ROOT>,

<&clk IMX8MQ_CLK_DUMMY>;

clock-names = "disp-axi", "csi_mclk", "disp_dcic";

status = "disabled";

};

2. what is link-frequency from above picture ?

is it a MIPI_CLK or MIPISCLK?

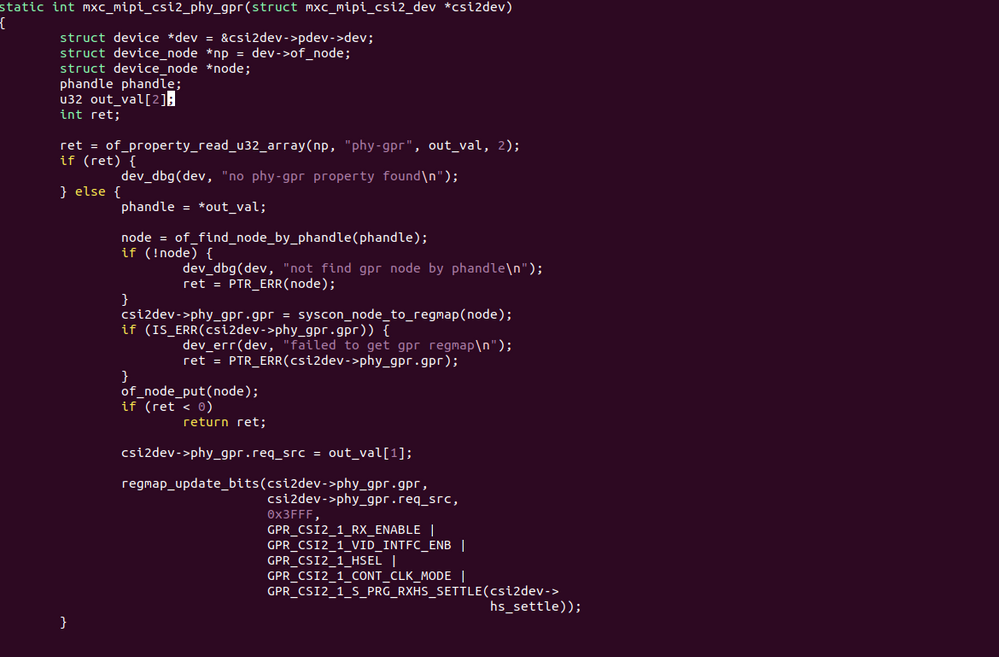

3. To set link frequency other MHZ ( ex, 300Mhz ) , then how should we modify MIPI CSI2 host Controller - mxc-mipi-csi2_yav.c ?

static void mxc_mipi_csi2_hc_config(struct mxc_mipi_csi2_dev *csi2dev)

{

u32 val0, val1;

u32 i;

val0 = 0;

/* Lanes */

writel(csi2dev->num_lanes - 1,

csi2dev->base_regs + CSI2RX_CFG_NUM_LANES);

for (i = 0; i < csi2dev->num_lanes; i++)

val0 |= (1 << (csi2dev->data_lanes[i] - 1));

val1 = 0xF & ~val0;

writel(val1, csi2dev->base_regs + CSI2RX_CFG_DISABLE_DATA_LANES);

/* Mask interrupt */

writel(0x1FF, csi2dev->base_regs + CSI2RX_IRQ_MASK);

writel(1, csi2dev->base_regs + 0x180);

/* vid_vc */

writel(1, csi2dev->base_regs + 0x184);

writel(csi2dev->send_level, csi2dev->base_regs + 0x188);

}

static int mipi_csi2_clk_init(struct mxc_mipi_csi2_dev *csi2dev)

{

struct device *dev = &csi2dev->pdev->dev;

csi2dev->clk_core = devm_clk_get(dev, "clk_core");

if (IS_ERR(csi2dev->clk_core)) {

dev_err(dev, "failed to get csi core clk\n");

return PTR_ERR(csi2dev->clk_core);

}

csi2dev->clk_esc = devm_clk_get(dev, "clk_esc");

if (IS_ERR(csi2dev->clk_esc)) {

dev_err(dev, "failed to get csi esc clk\n");

return PTR_ERR(csi2dev->clk_esc);

}

csi2dev->clk_pxl = devm_clk_get(dev, "clk_pxl");

if (IS_ERR(csi2dev->clk_pxl)) {

dev_err(dev, "failed to get csi pixel link clk\n");

return PTR_ERR(csi2dev->clk_pxl);

}

return 0;

}

can you inform me DPHY Register setting on IMX8M Quad ?

do we modify mipi_csi_1 clock setting from above mx8mq device tree ?

assigned-clock-rates = <133000000>, <100000000>, <66000000>;

4. finally, if we'd like to Raw8 bit from OV5640 , then should we modify capture driver - ov5640_mipi_v2.c ?

It seems to support RAW8Bit Bayer ( SBGGR8) by default .

cant you inform me how to setup CSICR1, CSICR2, CSICR3, CSI_CSIIMAG_PARA , CSICR18 registers ?

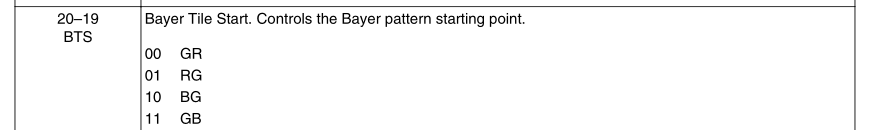

5. For CSICR2 setting, can you inform me how to set BTS (Bayer tile Start) at 5005 page from Reference manual ?

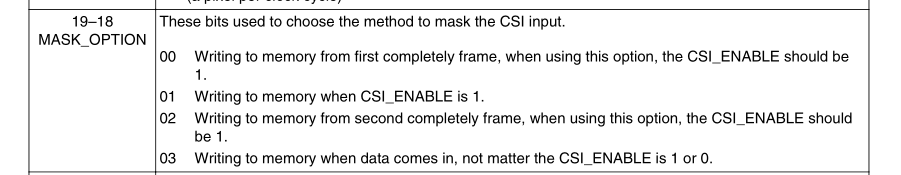

6. For CSICR18 setting , how to setup Mask_option ( 19-18 Bits ) at 5019 page from Reference Manual ?

Thanks .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JungHwan

for raw8 one can look at example below

https://community.nxp.com/t5/i-MX-Processors/iMX8M-MIPI-CSI-4-lane-configuration/m-p/875755

Best regards

igor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Frequency is MIPI Clock from Tovalds.

/* Calculate the line rate from the pixel rate. */

link_freq = v4l2_get_link_freq(state->src_sd->ctrl_handler, state->csi2_fmt->width, state->bus.num_data_lanes * 2);

s64 v4l2_get_link_freq(struct v4l2_ctrl_handler *handler, unsigned int mul,

unsigned int div)

{

struct v4l2_ctrl *ctrl;

s64 freq;

ctrl = v4l2_ctrl_find(handler, V4L2_CID_LINK_FREQ);

if (ctrl) {

struct v4l2_querymenu qm = { .id = V4L2_CID_LINK_FREQ };

int ret;

qm.index = v4l2_ctrl_g_ctrl(ctrl);

ret = v4l2_querymenu(handler, &qm);

if (ret)

return -ENOENT;

freq = qm.value;

} else {

if (!mul || !div)

return -ENOENT;

ctrl = v4l2_ctrl_find(handler, V4L2_CID_PIXEL_RATE);

if (!ctrl)

return -ENOENT;

freq = div_u64(v4l2_ctrl_g_ctrl_int64(ctrl) * mul, div);

pr_warn("%s: Link frequency estimated using pixel rate: result might be inaccurate\n",

__func__);

pr_warn("%s: Consider implementing support for V4L2_CID_LINK_FREQ in the transmitter driver\n",

__func__);

}

return freq > 0 ? freq : -EINVAL;

}

Then how do we set MIPI D-PHY Clock ?