- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: Setting EIM clock on 7D

Setting EIM clock on 7D

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Setting EIM clock on 7D

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I'm using a 7D board with a EIM interface to an FPGA. I have this working well with 6sl using 66MHz clock. On 7d, I tried to setup the 66MHz clock using devicetree as per below:

&weim {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_weim_cs2_1>;

#address-cells = <2>;

#size-cells = <1>;

/* <cs-number> 0 <physical address of mapping> <size> */

ranges = <0 0 0x28000000 0x02000000>, /* 32MB CS0 */

<1 0 0x2A000000 0x02000000>, /* 32MB CS1 */

<2 0 0x2C000000 0x02000000>, /* 32MB CS2 */

<3 0 0x2E000000 0x02000000>; /* 32MB CS3 */

status = "okay";

fsl,weim-cs-gpr = <&gpr>;

assigned-clock-rates = <66000000>;

imx-weim@2,0 {

compatible = "fsl,imx6q-weim";

reg = <2 0 0x02000000>;

#address-cells = <1>;

#size-cells = <1>;

bank-width = <2>;

fsl,weim-cs-timing = <0x00e10089 0x00001130 0x01010000 0x00000000 0x06040600 0x00000000>;

};

imx-weim@3,0 {

compatible = "fsl,imx6q-weim";

reg = <3 0 0x02000000>;

#address-cells = <1>;

#size-cells = <1>;

bank-width = <2>;

/* CSxGCR1, CSxGCR2, CSxRCR1, CSxRCR2, CSxWCR1, CSxWCR2. */

fsl,weim-cs-timing = <0x00e10089 0x00001130 0x02010000 0x00000000 0x06040600 0x00000000>;

};

};

The processing of that looks fine. I dumped the EIM_CS3/4 regs and they match the configuration values specified above. When I access the memory space, I get CS assertion and the transaction (aside from exact timing) looks reasonable.

The part that does not seem to work is the assigned-clock-rate. I've specified 66MHz above. But it does not seem to have any effect on the physical interface. Here's the timing that I get:

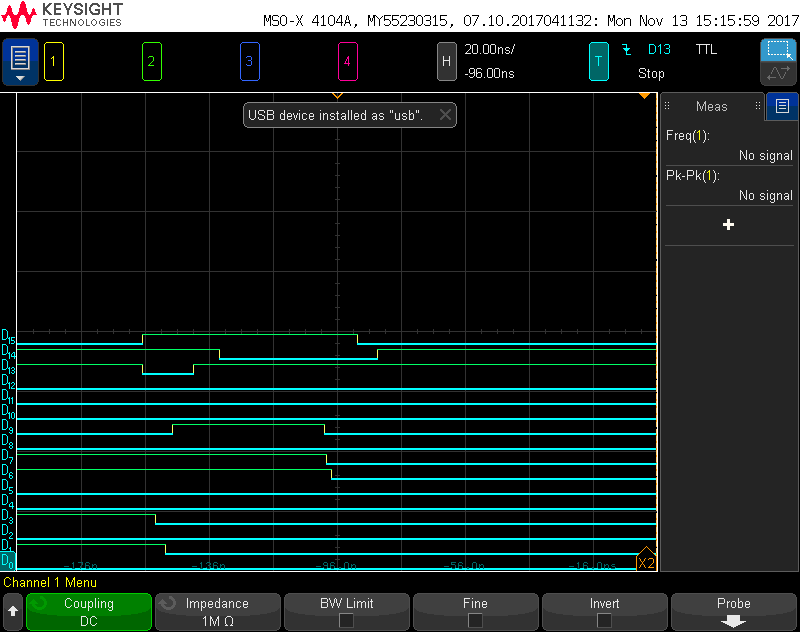

D15 is the chipselect. D11-D0 are address lines.

The total chipselect assertion time is only 65ns which is only 4 clocks at 66MHz! It should be about 350ns (which is what it is on 6sl).

Signals like LBA and Address phase seem out of sync (LBA gets asserted before address seems to be valid). This leads to me think that the core EIM clock is wrong.

imx7d.dtsi says:

weim: weim@30bc0000 {

compatible = "fsl,imx7d-weim", "fsl,imx6sx-weim", "fsl,imx6q-weim";

reg = <0x30bc0000 0x10000>;

interrupts = <GIC_SPI 13 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX7D_EIM_ROOT_CLK>;

status = "disabled";

};

I checked that the assigned clock rate seems to match what I set:

root@imx7dsabresd:~# hexdump -C /sys/firmware/devicetree/base/soc/aips-bus\@30800000/weim\@30bc0000/assigned-clock-rates

00000000 03 ef 14 80 |....|

00000004

root@imx7dsabresd:~# printf %d, 0x3ef1480

66000000

Is there a step or parameter that I have missed in order to setup the EIM clock.

I would welcome any advice or suggestions.

Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Was there a solution to this issue? I'm like to set the EIM clock to a non integer divisible value of the standard clocks. I would like to better understand how to manipulate the PLL frequencies as roots to the EIM to achieve this. the 480 MHz USB PLL is unused in our system. Are there instructions on how to modify these frequencies, if not how can I utilize an external clock to achieve what I need (43.75 MHz EIM bus freq).

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Actually, the EIM root clock selection setting seems to be wrong. Try to dump the EIM clock root slice register at the 0x3038A980 address and check its value. Typically, it should be either 1 (SYS_PLL_PFD2_DIV2 running at 135MHz as the root clock source), 2 (SYS_PLL_DIV4 running at 120MHz as the root clock source) or 6 (ENET_PLL_DIV8 running at 125MHz as the root clock source). The maximum EIM root clock frequency must not exceed 135MHz for the i.MX7Dual processor.

Have a great day,

Artur

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thanks for your reply.

- Dumping CCM_TARGET_ROOT83 (0x3038A980)

root@imx7dsabresd:~# /unit_tests/memtool -32 0x3038A980 1

E

Reading 0x1 count starting at address 0x3038A980

0x3038A980: 12000000

Therefore:

POST_PODF=0

PRE_PODF=0

MUX=2 => SYS_PLL_DIV4 so 120MHz

ENABLE=1 => clock root is on

In arch/arm/boot/dts/imx7d.dtsi, I see:

weim: weim@30bc0000 {

compatible = "fsl,imx7d-weim", "fsl,imx6sx-weim", "fsl,imx6q-weim";

reg = <0x30bc0000 0x10000>;

interrupts = <GIC_SPI 13 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&clks IMX7D_EIM_ROOT_CLK>;

status = "disabled";

};

which comes from:

clks[IMX7D_EIM_ROOT_SRC] = imx_clk_mux2("eim_src", base + 0xa980, 24, 3, eim_sel, ARRAY_SIZE(eim_sel));

clks[IMX7D_EIM_ROOT_CLK] = imx_clk_gate4("eim_root_clk", "eim_post_div", base + 0x4160, 0);

static const char *eim_sel[] = { "osc", "pll_sys_pfd2_135m_clk",

"pll_sys_main_120m_clk", "pll_dram_533m_clk",

"pll_sys_pfd2_270m_clk", "pll_sys_pfd3_clk", "pll_enet_125m_clk",

"pll_usb_main_clk", };

I don't see anything wrong in that. But clearly the assigned-clock-rate parameter is ignored. I also tried clock-frequency= eg:

clocks = <&clks IMX7D_EIM_ROOT_CLK>;

+ clock-frequency = <66000000>;

status = "okay";

fsl,weim-cs-gpr = <&gpr>;

assigned-clock-rates = <66000000>;

+ clock-frequency = <66000000>;

These too have no effect.

My desired EIM clock rate is 66MHz. I don't see anyway of how to set it to that using devicetree. Is this feasible or does this mean it is not supported by 7d imx-weim code meaning one has to manually set the CCM_TARGET_ROOT83 pre/post divider register?

Thanks and have a great day!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Seems not to be supported in device tree. Better seems to set the register manually.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Artur,

Thanks for your reply. I'm not sure it is 'better' but since seems like nobody will fix it in devicetree or imx-weim code, then I have no choice but to set it manually.

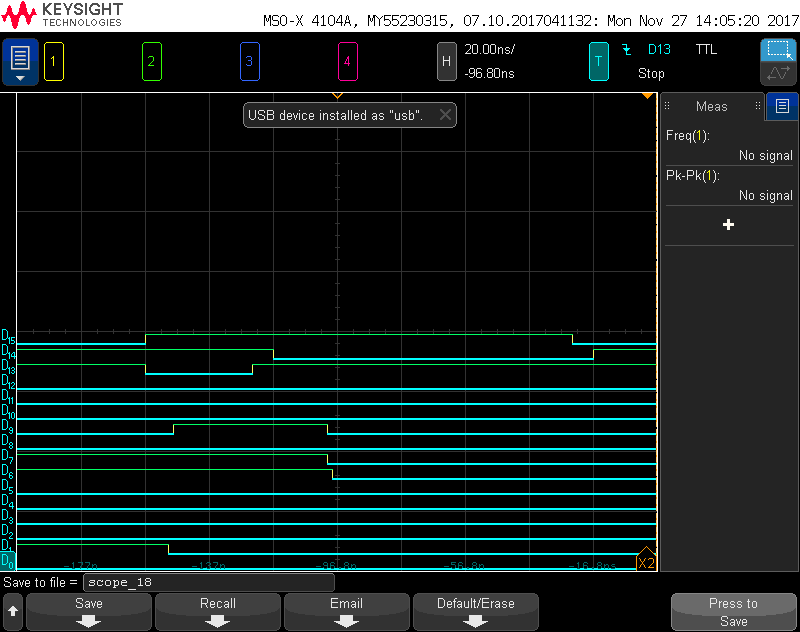

However, even when I set it manually, ie: by seting POST_PODF=1 , 0x3038A980: 12000001 , now EIM clock should be 60MHz (120/2), I still get bad behavior from the EIM signals. For example, the address signal AD14 (D1 in scope) and AD6 (D9 in scope) change late (7.5ns and 10ns) after EIM_LBA (D13 in scope) is already asserted. This results in FPGA latching wrong address since it has to use LBA as the address valid signal.

I checked that on 6sl, using the exact same EIM register settings, I do not get this behavior and AD signals change before LBA assertion. So it seems to be some problem specific to 7d. Here's my EIM register settings:

(EIM_CS3GCR1)

0x30BC0048: 00E10089

(EIM_CS3GCR2)

0x30BC004C: 00001130

(EIM_CS3RCR1)

0x30BC0050: 02010000

(EIM_CS3RCR2)

0x30BC0054: 00000000

(EIM_CS3WCR1)

0x30BC0058: 06040600

(EIM_CS3WCR2)

0x30BC005C: 00000000

If you have any suggestions what could be going wrong, please let me know. Thanks!