- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: SDRAM debugging is not happening on imxrt1051 processor target board

SDRAM debugging is not happening on imxrt1051 processor target board

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SDRAM debugging is not happening on imxrt1051 processor target board

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

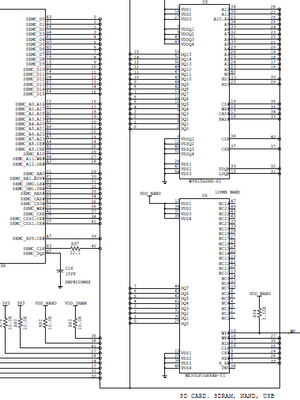

We have connected SDRAM and NAND flash on semc bus on MIMXRT1051CVL5B target board. And We could not able to debug in SDRAM with the JLink script provided in SDK. However, we could able to debug in EVAL kit but not on our target board.

Kindly suggest the changes required in the jlink link script file.

PFA files.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes , we have tested with the sample code evkbimxrt1050_semc on our target board and we able to read and write the from SDRAM but it is failing in the read write comparison.

The logs are attached.

SEGGER J-Link GDB Server V7.60b - Terminal output channel

SEMC SDRAM Example Start!

SEMC SDRAM Memory 32 bit Write Start, Start Address 0x80000000, Data Length 200 !

SEMC SDRAM Read 32 bit Data Start, Start Address 0x80000000, Data Length 200 !

SEMC SDRAM 32 bit Data Write and Read Compare Start!

SEMC SDRAM 32 bit Data Write and Read Compare Succeed!

SEMC SDRAM Memory 16 bit Write Start, Start Address 0x80000000, Data Length 4096 !

SEMC SDRAM Read 16 bit Data Start, Start Address 0x80000000, Data Length 4096 !

SEMC SDRAM 16 bit Data Write and Read Compare Start!

SEMC SDRAM 16 bit Data Write and Read Compare Failed!

SEMC SDRAM Memory 8 bit Write Start, Start Address 0x80000000, Data Length 4096 !

SEMC SDRAM Read 8 bit Data Start, Start Address 0x80000000, Data Length 4096 !

SEMC SDRAM 8 bit Data Write and Read Compare Start!

SEMC SDRAM 8 bit Data Write and Read Compare Failed!

SEMC SDRAM Example End.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @venkataddagatla ,

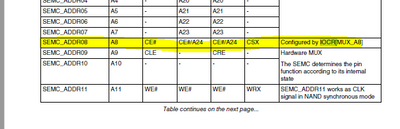

NAND Flash CE# is shared with SDRAM A8. This is not allowed. Because the pins function is configured by IOCR.MUX_A8. After SEMC is well initialized, this field can't be changed.

I have a W9825 DCD file. You can take a look.

Regards,

Jing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Actually we want to use SDRAM and NAND on Semc bus. We had assigned the pins as mentioned in the Pin mux of the semc module. That is the reason you have seen the SEMC_ADDR08 connects to A8 pin of SDRAM and the same goes to CE# of NAND flash and all other as same as mentioned in the doc.

Is it possible by properly configuring IOCR register we can able to operate both without issues?

Kindly suggest, as we want to run our application from SDRAM and want to store data in NAND flash in runtime. Will it be an issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for the response.

Do you mean only SDRAM should use that pin and remove from NAND. Can you help how we can interface both (SDRAM and NAND) on semc bus. Kindly share the example if you have any.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @venkataddagatla ,

Yes. IOCR can only be set during initialization. You can't change it frequently at run time. That doesn't make sense. But I can't find any other examples or cases like yours. Few new project use parallel NAND flash now.

Regards,

Jing