- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Need continuous BCLK?

Need continuous BCLK?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Need continuous BCLK?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am designing a product using the iMX6ULL. I need a clock to run my FPGA and cannot use

CCM Clock 1 or 2 since I am using SD card port 1 and I need the JTAG port operable. I am

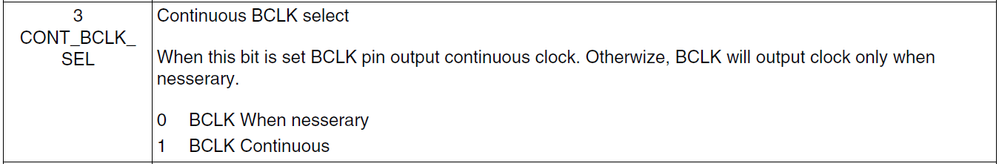

thinking of using EIM "BCLK" and have found the "CONT_BCLK_SEL" bit in the EIM_WCR register.

There seems to be a lot of discussion in the community whether BCLK can function like one of the

CCM_CLK, this is possible? Will it work for my MCIMX6Y2CVM08AB part? I would like to test this

signal on my Freescale iMX6ULL-EVK and would also like to know how to change the UBOOT/ LINUX

software to accomplish this function from startup? If "BCLK" is not continuously possible can you suggest

any other means of getting a continuous clock for the iMX6ULL part?

Thanks for reading and helping!

Larry

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Larry,

see below, please!

(1) About EIM_BLCK

yes, the clock can be configured as continous in register EIM_WCR

more detailed information ,see reference manual, please!

(2) Suggestion on clock for your FPGA's working clock

--- provided by CPU

The better choice is to get clock from CCM_CLKO1 & CCM_CLKO2.

--- Using external clock

probably FPGA requires higher precision clock, From a technical point of view, you can choose to meet the requirements of OSC or crystal, which has no risk.

(3) Signal transmission synchronous clock

If your FPGA is connected to EIM interface and use SYNC mode, it is no problem to use BLCK for FPGA. It is not recommended that you use BCLK as the working clock of FPGA.

Have a nice day!

BR,

weidong