- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: How to route an external MCLK to multiple SAIs

How to route an external MCLK to multiple SAIs

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to route an external MCLK to multiple SAIs

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Receive the external MCLK via SAIn_MCLK input pad

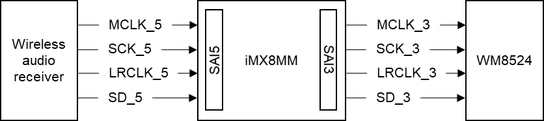

According to the iMX8MM reference manual, it is possible for both SAI5 and SAI3 to use the MCLK_5 as the master clock if MCLK_5 is fed to the SAI5_MCLK pad and the IOMUXC_GPR registers are configured accordingly. However, I don't see any document/examples about how to configure it correctly. I took a look at the Linux source files (e.g., fsl_sai.c, fsl_sai_sysfs.c), but it seems like such control is not implemented anywhere.

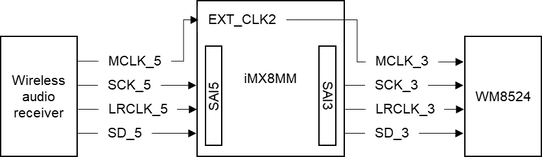

2) Receive the external MCLK via EXT_CLKn pin

Another possibility is to receive the MCLK_5 via EXT_CLK2 pin and distribute internally through the clock tree. But, the EXT_CLK2 pin is not readily accessible on the iMX8MM EVK. Also, it is less preferreable than the prior method of using the IOMUXC_GPR registers becuase we plan to involve additional SAI for our end appliaction. While the EXT_CLKn is shared between subset of SAIs, the IOMUXC_GPR-based method allows a complete flexibility in choosing the MCLK source.

[ Questions ]

Q1. So far, I was able to customize the kernel using 'simple-audio-card' to record (i.e., arecord) the audio stream coming from the wireless IC. However, I used the IMX8MM_AUDIO_PLL1_OUT as the MCLK. How can I use the MCLK_5 on SAI5_MCLK pad as the master clock? (FYI, the following is my device tree snippet).

/dts-v1/;

#include "imx8mm-evk.dts"

/ {

// wac: wireless audio codec

wac: wac {

#sound-dai-cells = <0>;

compatible = "test,wac";

status = "okay";

};

sound-wac {

compatible = "simple-audio-card";

simple-audio-card,name = "wac";

simple-audio-card,dai-link@0 {

format = "i2s";

bitclock-master = <&wac_dai>;

frame-master = <&wac_dai>;

wac_cpu: cpu {

sound-dai = <&sai5>;

};

wac_dai: codec {

sound-dai = <&wac>;

};

};

};

};

&sai5 {

#sound-dai-cells = <0>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_sai5>;

assigned-clocks = <&clk IMX8MM_CLK_SAI5>;

assigned-clock-parents = <&clk IMX8MM_AUDIO_PLL1_OUT>;

assigned-clock-rates = <1536000>;

status = "okay";

};

&iomuxc {

pinctrl_sai5: sai5grp {

fsl,pins = <

MX8MM_IOMUXC_SAI5_MCLK_SAI5_MCLK 0xd6

MX8MM_IOMUXC_SAI5_RXC_SAI5_RX_BCLK 0xd6

MX8MM_IOMUXC_SAI5_RXFS_SAI5_RX_SYNC 0xd6

MX8MM_IOMUXC_SAI5_RXD0_SAI5_RX_DATA0 0xd6

>;

};

};

Q2. Once the Question 1 has been addressed, how and where can I configure the IOMUXC_GPR registers to use SAI5_MCLK (i.e., MCLK_5) as the master clock for the SAI3?

Q3. In another thread, it says that the system hangs during the boot if a clock is not present on EXT_CLKn pin. Is it the expected behavior? In other words, should the MCLK_5 be available before the system boot and be always present?

Q4. I wonder if the same or similar issue as Q3 is also present in the case of using the SAIn_MCLK pad to feed the external clock. Does MCLK_5 have to be present all the time before the system boot and while the system is operating?

Q5. Continued from Q4, what happens if we activate SAI3 (e.g., aplay) while MCLK_5 is not present?

Thanks,

Woosuk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

For Q2:you should use

MX8MM_IOMUXC_SAI3_MCLK_SAI5_MCLK

, this config will let SAI3_MCLK select SAI5_MCLK as an input source.

For Q3 and Q4 ,I need some time to find if that patch has been merged to our latest BSP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Zhiming_Liu Thanks for the reply.

Q1) I confirmed that the wireless audio receiver outputs the MCLK_5 before getting connected to the iMX8MM EVK. But it disappears after connected to the EVK. It seams that the SAI5_MCLK pad is set to an output probably because the clock setting in my device tree was incorrect. Although SAI5 is working well as a slave without the MCLK_5, it is important to receive MCLK_5 so that it can be routed to MCLK_3 output.

- Could you please share an example how to properly configure the device tree to receive an external MCLK to SAI5?

Q2) I tried your suggestion, but no luck. Page 3896 of the iMX8MM RM says that the IOMUX_GPR registers have to be configured to use alternative MCLK options.

- By specifying below, does it take care of the IOMUX_GPR settings as well? Which function/source file should I look at to observe the configuration process?

MX8MM_IOMUXC_SAI3_MCLK_SAI5_MCLK- Could you please share a device tree snippet showing how to route MCLK_5 input to MCLK_3 output?

Q3/Q4)

- Do you have any update on this?

- Could you please share a link to the patch details?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Q1: According to RM, bit clock can be set as externally generated. Can you set it manually with memtool? The register address is 30050090 for SAI5 RCR2, Bit Clock Direction, you can see the explanation for MCLK Select.

Q2:MX8MM_IOMUXC_SAI3_MCLK_SAI5_MCLK mux sai3_mclk pad as sai5_mclk , the sai3_mclk is sai5_mclk.