- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: How PF1550 can discharge lithium battery only when VBUSIN is lost?

How PF1550 can discharge lithium battery only when VBUSIN is lost?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How PF1550 can discharge lithium battery only when VBUSIN is lost?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a design with a PF1550 PMIC. System is powered by a main power feeding VBUSIN almost permanently and a rescue lithium-ion battery. Our goal is to keep our rescue battery charged in case main power is lost, in order to improve power-cut autonomy. For this reason, we want PMIC to use VBUSIN first, and VBATT only when VBUSIN is lost or weak.

But when our board is powered by both main-power and a charged rescue battery in our standard configuration (CHG_OPER[1:0] = 2), both are actually used to power the system shortening our power-cut autonomy. Worst, this also occurs when we stop the charger (CHG_OPER[1:0]=1) (we must do it explicitly in a few cases to avoid any charge above +45°C otherwise we do not pass certifications). In this second case our rescue battery appears to obviously empty itself.

Does PF1550 features an option to not use lithium-ion source when VBUSIN source is available? I fail to find it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Got an answer from the related NXP ticket support, sharing it:

My first issue is that when charger is off, then both power sources appears used by my PMIC to supply the system, instead of main power source only since my board consumes less than 100 mW globally (very easy for my VBUSIN).

For PF1550 A6, VSYS=3.7V, generally Li-Ion battery CHGCV=4.2V, when VUBSIN limit is not triggered and charger is OFF (CHG_OPER[1:0]=2’b01 means Charger OFF, Linear ON), VBATT and VSYS are still connected through BATFET, if VBATT < VSYS, small leakage (~60uA) current from VBATTà VSYS; once VBATT voltage is higher than VSYS, there’s some current of VBATTà VSYS, it is proportional to the delta voltage between VBATT and VSYS.

Since the “Charger OFF, Linear ON” is designed to application cases without battery, hence we didn’t describe this with battery attached situation.

Generally, setting VSYS=4.3V > CHGCV=4.2V (VSYS always > VBATT) is recommended.

My second issue is that I think I saw this same kind of issue when charger was enabled (but battery fully charged)

For PF1550 A6, VSYS=3.7V, generally Li-Ion battery CHGCV=4.2V, when VUBSIN limit is not triggered and charger is ON (CHG_OPER[1:0]=2’b10 means Charger ON, Linear ON), VSYS and VBATT are connected through BATFET, VSYS voltage will not be constant as 3.7V during charging, when charging is in Done status (charging is complete), VSYS voltage keep a little higher than CHGCV=4.2V and VSYS is the prior power source.

We don’t see the current VBATT->VSYS in Done status, this should meet customer requirement.

While setting VSYS=4.3V > CHGCV=4.2V (VSYS always > VBATT) is recommended.

My first tests with VSYSMIN set to 4.3V (and CHGCV unchanged 4.2V) are successful :smileyhappy:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

1:Do you mind show your schematic for us?

2: Could you please test the VSYS and Vbat waveform when Vbat involved in provide power to system?

3: Do you check VBUS input terminal current? Does VBUS input terminal have enough current capacity?

4: How do you realize the battery fully charged? which register do you check?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

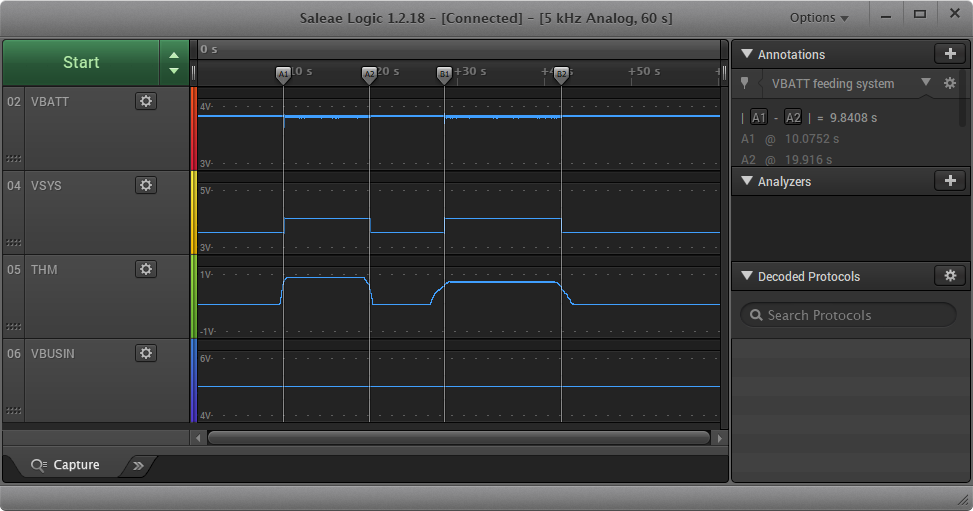

I sent you my schematic and my measurements details in the private support case 00217962. Here is a screenshot of on of those measurements:

In this screenshot we can see VBATT supplementing the system as soon as its thermal resistor indicates a usable battery.

I am confident my VBUSIN can feed required energy since my board can run in much more high power consumption through VBUSIN (when my main processor is not suspend and when I enable my GNSS chip).

Also, most of the time I simulate my battery with an external power source and a potentiometer instead of the NTC. When I speak about fully charged battery I am thinking about cases where a real battery was plugged all previous night. I was not reading PMIC registers to check.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

A few more technical notes: when my main processor is suspended, my PMIC is in standby. I enabled low-power flag on SW1/SW2/VREFDDR/LDO1/LDO2/LDO3 lines and I setted up SW3 to be off for PMIC to join lower power consumptions in standby

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

I can't copy your issue,I will discuss this issue with my colleague next!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

We only have function of Battery supplement mode about PF1550.

You can get conclusion that when the load of VSYS increase enough then VSYS decrease, at same time VBATT involved in and provide current to support the VSYS load together with VBUS.

So we can't configure PF1550 to use only BATTERY source in application.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not looking to use VBATT only, but instead to use VBATT only when required (only when VBUSIN is too weak).

In my main issue case, I am running in low power (PMIC charger off, iMX6 processor suspended waiting for an event) and my power consumption is very small (board consumes 6mA@12VDC if only main powered, 3.5mA@4VDC when only VBATT-powered - which is fine). When both sources are plugged, I would expect my system to only drain 6mA@12VDC and noting onto VBATT but it actually consumes 4mA@12VDC plus 7mA@4VDC.

I plugged a potentiometer on VBATT thermal bounds and this issue appears and disappear as soon as thermal resistor indicates a usable or a not-usable battery. I can play with this potentiometer during my low power modes and see the issue appearing and disappearing accordingly.This thermal wiring is exclusively routed to PF1550 of course.

My understanding of PF1550 specifications is that battery supplement mode should only drain VBATT when VBUSIN lacks energy to feed VSYS, but my measurements let me think that VBATT is drained when VBUSIN should be around 15 mA max (regulated to 5VDC from the 12VDC main power source) which is far less than the current limitation set to 400 mA.

I have dumped my PMIC registers before joining my low power mode. I can provide them if this can help.

Note: IIRC I seen the same issue when my system is up (charger enabled) and my battery fully charged, but I am less worried about this for now since I hope PMIC would re-start charging before battery goes low.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI

I am sorry that I can't fully understand your issue points.

Could you please list your issue one by one?

For your questions--My understanding of PF1550 specifications is that battery supplement mode should only drain VBATT when VBUSIN lacks energy to feed VSYS, but my measurements let me think that VBATT is drained when VBUSIN should be around 15 mA max (regulated to 5VDC from the 12VDC main power source) which is far less than the current limitation set to 400 mA.

---

You can verify your current limit set correct or wrong by checking read register- VBUS_LIN_ILIM[4:0] setting.

You can also double check your VBUS input source whether VBUS has enough carry load capacity.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- My first issue is that when charger is off, then both power sources appears used by my PMIC to supply the system, instead of main power source only since my board consumes less than 100 mW globally (very easy for my VBUSIN).

- My second issue is that I think I saw this same kind of issue when charger was enabled (but battery fully charged)

I checked the value of register VBUS_INLIM_CNFG (address 0x80+0x14=0x94). It equals 0xa0 (meaning VBUS_LIN_ILIM=20, limitation set to 1500 mA) whereas specifications announces a default of 0x68 for this register (VBUS_LIN_ILIM=13, limitation set to 400 mA). This is very weird that my PMIC does not features expected default value...

But if we close our eyes on this weirdness, such a huge limitation should never trigger supplement mode in my case.

I have a full register dump if required, I can give you of them. If useful, first registers are as this:

00: 7c

01: 06

02: 11Meaning this is a PF1550 A6 as expected, metal_layer_rev=1, full_layer_rev=1, fab_fin=0.